|

ASIC and FPGA Design Undergraduate

Courses |

Introducción a DIE/DEPSE DIE:

Dispositivos Integrados Especializados (Grado Telecom) DEPSE:

Desarrollo de Procesadores y Sistemas Específicos (Grado Informática) |

|

Site

Map Academic Courses: Publications: R&D / Industry: EUROFORM Technical Training for Industry Android: Technical Conferences: Journals: Joining the Lab: Sabbatical

year, Master or PhD Degree at the DSLab UAM? |

1. Introducción: Esta asignatura es el primero

contacto del estudiante de la EPS con la tecnología FPGA. Proporciona el

entrenamiento necesario para trabajar inmediatamente en las diversas empresas

nacionales y europeas que utilizan este tipo de circuitos. Existe un ávido mercado local de

trabajo para aquellos que se especialicen en dispositivos programables. España sin duda es un país dado a las

FPGAs. La relación se origina en la escasa implantación en la industria

local, de tecnologías alternativas como Gate Arrays o Standard Cells, que ya existían en la

década de los 80. Los ingenieros

españoles acogieron la lógica programable sin pre-conceptos, y sin la

necesidad de descartar tecnologías que de otro modo estarían formando parte

de sus productos. En otros países, los usuarios de FPGAs debieron vencer

durante años la resistencia de los especialistas en las tecnologías que estos

dispositivos iban a reemplazar. Adicionalmente, hubo una rápida incorporación

de estos chips en la docencia de grado. En 1989 ya eran obligatorios en el

Laboratorio de Electrónica Digital de la ETSIT-UPM [1]-[3]. El nombre DIE es una traducción

libre de ASIC, que significa Application-Specific

Integrated Circuits. Es decir, (circuitos

integrados a medida). La palabra ASICs como tal fue

descartada para no denominar en inglés una asignatura del plan de estudios.

Pero en la EPS UAM se cumple que: DIE = ASICs = Tecnologías FPGA y Standard Cells En España, un cuatrimestre

académico debe entenderse como unas 13 semanas. En el primero de ellos están

las fiestas de fin de año y en el segundo la Semana Santa. Y en ambos,

festivos históricos, religiosos y gremiales (“San Teleco”). Por lo tanto, DIE

se limita a: ·

13 x 3 = 39 hs de Teoría ·

13 x 2 = 26 hs de Lab En total, unas 65 hs. Aunque esta cifra no es suficiente para formar un

diseñador/a de circuitos integrados, es posible aprender bastantes cosas, si

se aprovecha el tiempo. A modo de ejemplo, un primer curso de piloto de

avioneta ocupa unas 100 hs de clases teóricas y 45

de vuelo (el Laboratorio) [5]. 2. ¿Qué es una FPGA? [4] La idea de fabricar un ASIC

programable por el usuario estaba madura en la década de los ´80. Las

primeras FPGAs originariamente se llamaban LCAs (Logic Cell Arrays), y habían salido al mercado en 1985. En

España eran casi desconocidas pero utilizadas por empresas punteras como

PESA. La nueva idea era sencilla y se basaba en 3 conceptos conocidos: ·

Utilizar multiplexores para realizar funciones lógicas,

en lugar del típico arreglo de transistores P y N. Esta técnica era enseñada de generación en

generación a los estudiantes de Circuitos Lógicos desde la época de los TTL,

pues que permitía ahorrar chips,

soldaduras y pistas. ·

Hacer una interconexión programable on-chip

inspirándose en la red telefónica. Ésta era una innovación también era

sencilla y estaba a la vista de todos de la época, La red telefónica (la de

los cables de cobre) no requería tender un hilo fijo entre cada par de

abonados. En su lugar, existía una interconexión matricial de cables que se

iban conectando mediante conmutadores hasta formar una unión galvánica entre

los puntos a enlazar. Lo que valía para teléfonos también valdría para los

circuitos integrados: no era necesario realizar la metalización fija final de

los masked-programmed chips para mapear un diseño

particular sobre la estructura estándar. Sólo se necesitaba difundir un

patrón de segmentos de pistas junto con recursos de interconexión

programables como multiplexores y llaves CMOS. ·

La última idea de las FPGAs era consecuencia de las anteriores:

una memoria almacenaría todos los valores de configuración del dispositivo.

En el caso de Xilinx, esta memoria era externa y se utilizaría una cadena de scan-path para

ingresar los bits que debían configurar tanto los multiplexores que mapeaban

las funciones lógicas y los elementos que rutaban señales internas. Altera

sorteó el problema mediante una EPROM interna, Lattice

con una EEPROM también interna, y Actel con antifusibles.

Sin embargo, el inconveniente de la propuesta de Xilinx no produjo rechazo

alguno: la utilización de una EPROM auxiliar para arrancar un circuito

programable complejo resultaba cotidiana para los miles usuarios de

microprocesadores. Las FPGAs fueron inventadas con la

idea de evitar los riesgos de fabricar un masked-ASIC. Esto era parecido (y sigue siéndolo) a escribir un

programa que se puede compilar una única vez. La reconfigurabilidad

se consideraba una característica esencial para poder corregir los errores de

diseño. Pero hubo muchas sorpresas. Poner a disposición de miles de

ingenieros e investigadores un producto como la FPGA, que permite probar

soluciones sin más coste que el tiempo que lleva implementarlas, fue como

soltar conejos en Australia. Diseñadores inquietos encontraron aplicaciones

muy prácticas. Por ejemplo: ·

Los usuarios de µP y DSPs

descubrieron que solidificar los algoritmos en el silicio producía unas

aceleraciones muy importantes. Poner 100 multiplicadores en lugar de pasar

100 veces los datos por el multiplicador de la ALU del procesador realmente cambiaba

la cosa. Nacen los primeros custom DSPs. ·

Ingenieros de computación montaron decenas de FPGAs en

tarjetas, junto con memorias, FIFOS y matrices de conmutación, de modo de

poder abordar problemas de mayor tamaño. Surge un nuevo acrónimo, FCCMs (FPGA-based

custom computer machines), para indicar

supercomputación a precios populares. ·

El hardware upgrade sólo requería podía enviar a un cliente una

nueva EPROM o reconfigurar de manera remota. ·

Se podía hacer que un equipo realice diferentes

funciones a lo largo del tiempo (entre ellas, auto-verificarse) simplemente

mapeando diferentes configuraciones e ideando un mecanismo de carga. Si estas

reconfiguraciones obedecían a causas externas, entonces se podía pensar en

circuitos adaptativos e incluso evolutivos. ·

Un procesador podía configurar una FPGA auxiliar antes

correr un programa, obteniendo así un coprocesador a medida, con las

funciones especiales requeridas para el cómputo. Después de un autotest, se podía reprogramar la FPGA

para evitar una parte defectuosa del chip,

creándose así un hardware cicatrizable. ·

Los directores de producción descubrieron que la programabilidad de los dispositivos también era crucial

para poder manejar el stock de

componentes en áreas como las telecomunicaciones, donde los cambios de

estándares son vertiginosos. Hoy en día la tecnología FPGA es

omnipresente en comunicaciones, discos duros, automoción, cómputo intensivo,

aplicaciones militares y de consumo. Las desventajas en velocidad y energía

respecto a un masked-ASIC se compensan de dos modos: ·

Las compañías de FPGAs, todas fabless, acceden en primer

lugar a las fábricas con tecnologías más avanzadas debido a su volumen y la

regularidad de sus circuitos. ·

Los chips de las FPGAs en si no son totalmente

configurables; tienen partes fijas. Es decir, incluyen bloques hardwired

dentro del chip (RAM, multiplicadores, controladores PCI, ADC, etc). Así, el campo de aplicación aumenta año tras año. A

ello se suman las nuevas combinaciones on-chip de procesador más FPGAs, que una y otra vez aparecen en la

historia de estos dispositivos. 3. Qué diferencia existe entre CED y DIE? CED es

el primer curso en diseño lógico. Se presentan conceptos básicos de Álgebra

de Boole y la estructura de los bloques básicos combinacionales y

secuenciales. La dificultad del laboratorio es la que corresponde a la

construcción de circuitos simples, de unas decenas de puertas. No se

enfatizan aspectos físicos como el tamaño, el retardo o el consumo de

potencia. DIE

trata de circuitos digitales de tamaño medio (decenas de miles de puertas y FFs). El retardo de los circuitos y sus problemas de

sincronización son el núcleo central de la asignatura. El laboratorio se

caracteriza por el uso exhaustivo de herramientas EDA profesionales. 4. Objetivos de la Asignatura Los conocimientos que se deber aprender después del curso son: ·

Capacidad para especificación, negociación o diseño de

un ASIC. ·

Conocimiento de la jerga de microelectrónica. ·

Practicar la codificación de VHDL sintetizable. ·

Técnicas para reducir retardo en FPGAs. ·

Realizar pruebas físicas sobre FPGAs. ·

Nociones de técnicas para facilitar la simulación y el

test de circuitos. ·

Principio

de Diseño Síncrono ·

Manejo optimizado de herramientas EDA. La mayoría de las carreras de Ingeniería incluyen algunas

asignaturas sobre el diseño de circuitos integrados, si bien el enfoque y la

tecnología en que se apoyan es variado. La

separación del diseño lógico en dos partes “Logica

Digital” (primer año de la EPS) y “Sistemas Digitales” también ha sido

propuesto en el resumen de las actividades del ACM/IEEE-CS Joint Curriculum Task Force 1991, donde

también figura una asignatura “Diseño de Sistemas VLSI” como curso avanzado

de grado. 5. Temario Introducción a los ASICs: La última parte del acrónimo FPGA significa Gate Array. Por ello, es

preciso comenzar por esta tecnología semicustom explicando su origen, ideas, y la jerga

microelectrónica. Todos estos aspectos han influido y se han colado en la

tecnología FPGA. ·

ASICs: Application Specific Integrated Circuit. ·

Proceso de

Fabricación. ·

Transistor

MOS. Gate Array. ·

Problemas de

los masked-ASICs. Introducción a las FPGAs: Este tema se desarrolla a lo largo del curso, pero es

necesario un resumen inicial para mitigar la desorientación de los/las

estudiantes en el lab. Básicamente, saber cómo es aproximadamente por dentro

una FPGA y a qué corresponde cada uno de los pasos que se ejecutan al

utilizar la herramienta EDA del lab.

·

Historia de

Xilinx Inc. ·

Ideas para

una FPGA: LUTs, Interconexiones y Memoria de Configuración. ·

Estructura de

una LUT. ·

Tipos de

Configuración ·

Arquitectura

de FPGAs Xilinx: Slices ·

Estándares de

I/O y BW. ·

Encapsulados ·

Bloques

Embebidos, soft-macros y Cores IP ·

Diagrama de

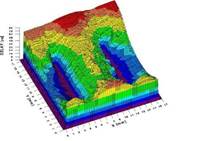

flujo de diseño. Herramienta EDA, Herramientas de síntesis ad-hoc. Retardos en Circuitos Integrados: En tecnología FPGA, el retardo de una operación lógica

está en el orden de decenas de picosegundos mientras que el de una pista

puede alcanzar varios ns. Es decir, un factor mayor

a mil veces. Es evidente que diseñar bajo estas condiciones (diametralmente

opuestas a las que había en el lab de CED de primero de la EPS UAM) requiere

conocer por qué aparecen estos retardos, que problemas genera y cómo

humildemente tratar de mitigarlos, considerando un modelo RC. ·

Capacidad.

Carga a corriente constante. Carga a corriente constante. Energía almacenada

en un condensador. ·

Valores

típicos de C en circuitos integrados. ·

Retardos

intrínsecos y extrínsecos. Fanin y Fanout. ·

Datos de una

célula SC ·

Señales

globales (broadcasted)

y cómo limitar el fanout

de un circuito ·

Compromiso area-time. ·

Retardos en

Xilinx ·

Árbol de

Reloj: Diseño en 0.18μ. Distorsión de Duty-Cycle. Digital Clock Manager. ·

Timing Analyzer, false-path y Caminos Críticos (Critical Path) ·

Deration con T y Vdd ·

Miscellaneous:

Pull-Up / Pull-Down, Bus keeper ·

Retardos

asíncronos Sincronización en Circuitos Integrados: Es continuación del tema anterior. Explica las

consecuencias de mezclar millones de FF con frecuencias de operación de

centenas de MHz. Se presenta el árbol de reloj, el principio de diseño

síncrono, los fallos de sincronización y las ideas para enganchar en fase

relojes internos y externos. Si hay tiempo adicional, se estudia la metaestabilidad y la sincronización entre dominios de

reloj.

·

Actividad

espuria (glitches).

·

Glitches en circuitos combinacionales. ·

Registros de

sincronización. ·

Parámetros

temporales de un FF ·

Gated-clocks: “relojes gateados” ·

Skew (Torcido) de reloj. Valores. ·

Fallos de

sincronización: captura nula y doble captura. ·

Principios de

Diseño Síncrono ·

Metaestabilidad. Pipelining Construir pipelines, el método más sencillo, directo y

potente para acelerar un circuito en FPGA. Fue tema de investigación en la

EPS UAM hasta que las FPGA la transformaron en una técnica cotidiana de

diseño. En el Lab se realiza un multiplicador pipeline y en la teoría se

revisan conceptos y limitaciones. ·

Ideas y

Conceptos Básicos ·

Velocidad (Throughput) y

latencia. ·

Aceleración (speed-up) y penalización en área. ·

RCA

segmentado. ·

Registros de skewing y

deskewing ·

Granularidad,

Profundidad de Lógica. ·

Coste de un pipeline. ·

Arrays segmentados para multiplicación. ·

Efecto de los

retardos de pista y FF sobre la eficiencia del pipeline. ·

Retiming. ·

Composición

del periodo de un pipeline real.

Ley de los Rendimientos Decrecientes. ·

Comunicación

local y global (broadcasted). Algoritmos EDA: Nociones de Síntesis, Particionado, Emplazamiento y

Rutado. No es un tema central en DIE, pero ayuda al diseñador a entender las

opciones que no son default en la

herramientas

·

Netlist. ·

Simplificación.Síntesis, Particionado, Emplazamiento y Rutado. ·

Uso de subexpresiones ·

Cofactoreo de Shanon ·

Método de

fuerzas ·

Método de Steimberg ·

Mincut ·

Simulated Annealing ·

Rutado global

y detallado ·

Principales

opciones de diseño manual de la Herramienta ISE Diseño para Testabilidad: Al igual que

en el tema anterior, se presentan las ideas primarias de “Testabilidad”. En

algunos casos son importantes, pero en otros, la reprogramabilidad

de las FPGAs permite obviarlas. ·

Bugs en

Circuitos Integrados ·

DFT = Design for Testability. ·

Técnicas

Heurísticas y Sistemáticas. ·

Test

Exhaustivo ·

Observabilidad y Controlabilidad ·

Modelo Stuck-at. Cobertura de fallos ·

Test de FSMs:

Scan Path ·

Temperatura y

fallos. ·

Chipscope. ·

Instrumental

de Verificación. 6. Referencias 1. E. Boemo, J. Meneses,

G. González de Rivera and F.

Barbero. "Field Programmable Logic in Education. A Case

Study", in More FPGAs,

W. Moore and W. Luk (eds.),

pp.452-457. Abbingdon EE&CS Books: Oxford

1994. [PDF] 2. E. Boemo and J. Meneses. "Learning VLSI using FPGAs", Proc. 23rd IEEE Frontiers in Education

Conference, pp.422-425. Washington, November 6-9, 1993. [PDF] 3. E. Boemo, J. Meneses,

F. Barbero and G. Gonzalez.

de Rivera, "Digital Design using LCAs. Results of an Educational Experiment at the School of Telecommunication

Engineering - UPM", Proc.VII DCIS Conference (Design of Circuit and

Integrated Systems), pp.217-221,

Universidad Politécnica de Madrid: November 1992. (in spanish) 4. E. Boemo, Prólogo del Libro de Actas de las

XI Jornadas de Computación Reconfigurable y Aplicaciones (JCRA'11),

Universidad de La Laguna, 2011. [PDF] 5. http://www.coptering.com/ 2016. |