|

ASIC and FPGA Design Undergraduate

Courses |

Open DIE/DEPSE de Placement DIE:

Dispositivos Integrados Especializados (Grado Telecom) DEPSE:

Desarrollo de Procesadores y Sistemas Específicos (Grado Informática) |

|

Site

Map Academic Courses: Publications: R&D / Industry: EUROFORM Technical Training for Industry Android: Technical Conferences: Journals: Joining the Lab: Sabbatical

year, Master or PhD Degree at the DSLab UAM? |

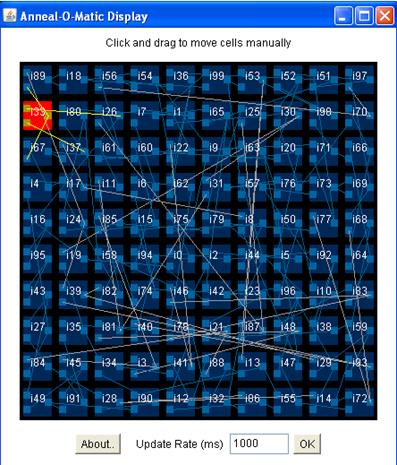

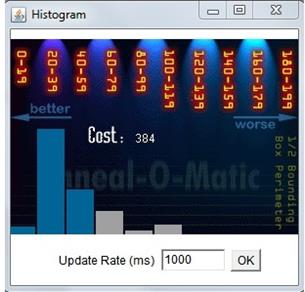

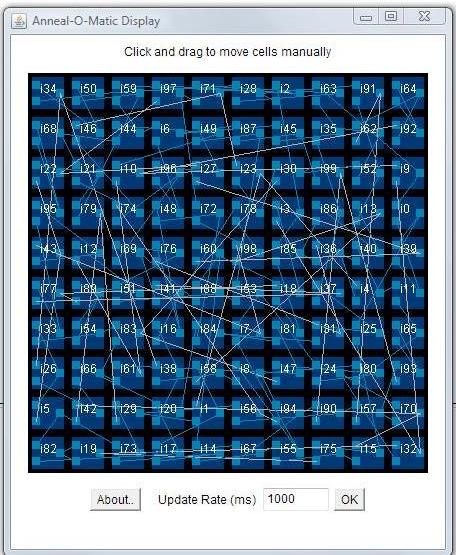

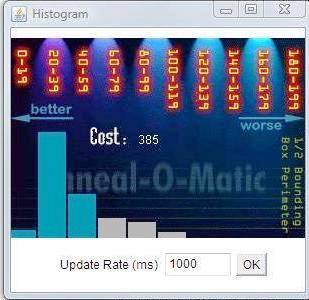

Introducción Las

dificultades de realizar un buen placement

se experimentan rápidamente probando unas cuantas configuraciones en el

sencillo circuito propuesto por S. Szollar y J.

Young de la UC Berkeley.

Anualmente

después de la clase de Herramientas EDA, comienza la célebre competición

EPS-UAM sobre optimización mediante el simulador de Annealing

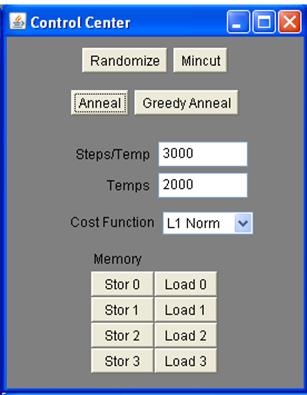

de Szollar y Young. Los competidores pueden probar

modificar los parámetros del Annealing, realizar un Mincut o mezclar dichas ideas

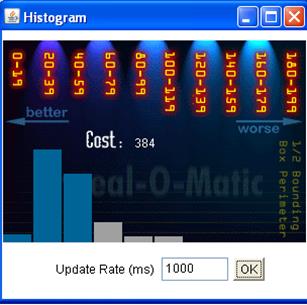

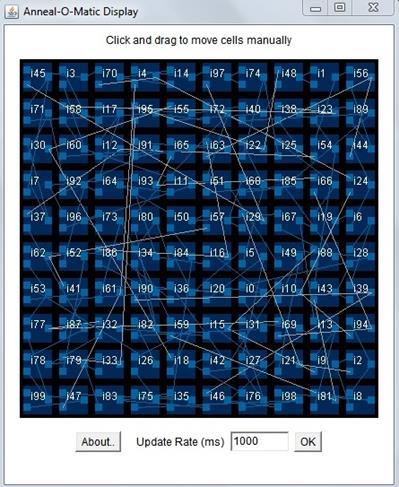

con un proceso manual. Los mejores resultados no han bajado de la barrera de

384. Una vista rápida a los mismos también evidencia que un buen placement produce una distribución

Pareto-Levy de retardos. Utilización del Anneal-O-Matic Puede

ejecutarse en: http://arantxa.ii.uam.es/~cedeps/anneal-o-matic/anneal.html pero

primero debe indicarse la dirección anterior como excepción en el Panel de

Control de Java, en el submenú Seguridad. Mejores resultados

Carlos Garcia Saura

(DIE 2012)

David Agra Robles, DIE 2012

Fahim Fernández, Nasib,

DIE 2010-11 |