SISTEMA DE DESARROLLO

(página en permanente cambio)

El hardware del Sistema de Desarrollo está formado por tres tarjetas:

Tarjeta de evaluación: es el modelo AT91EB55, basada en el microcontrolador AT91M55800A, de ATMEL. Está basado en el ARM. Se presenta el modelo de programación del microcontrolador y una descripción de sus periféricos y el modo de programarlos. Descripción del ensamblador y Conjunto de Instrucciones. Más descripciones del ensamblador.

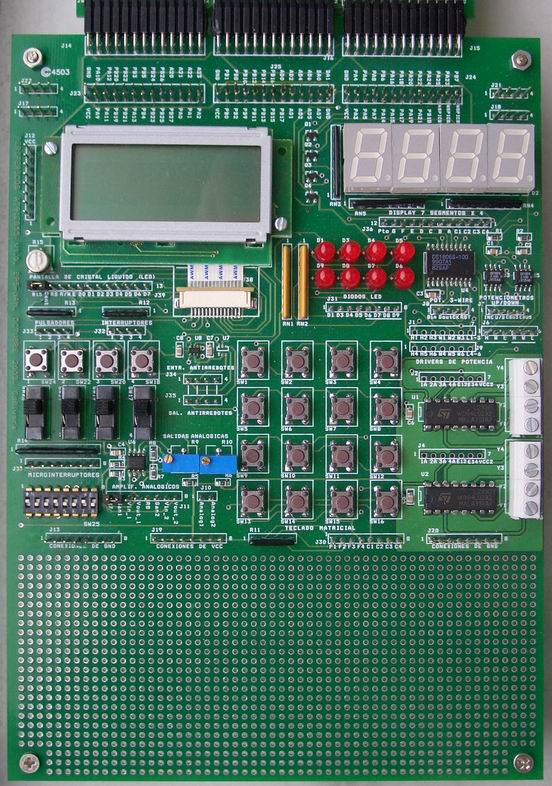

Tarjeta de Periféricos: en esta tarjeta, diseñada en la Escuela Politécnica Superior de la UAM, se incluyen una serie de periféricos de propósito general, como son LEDs, pulsadores, teclado, pantalla LCD, etc. Se conecta al bus de E/S de la tarjeta anterior y permite conectar cualquier periférico con cualquier pin de cualquier puerto del microcontrolador.

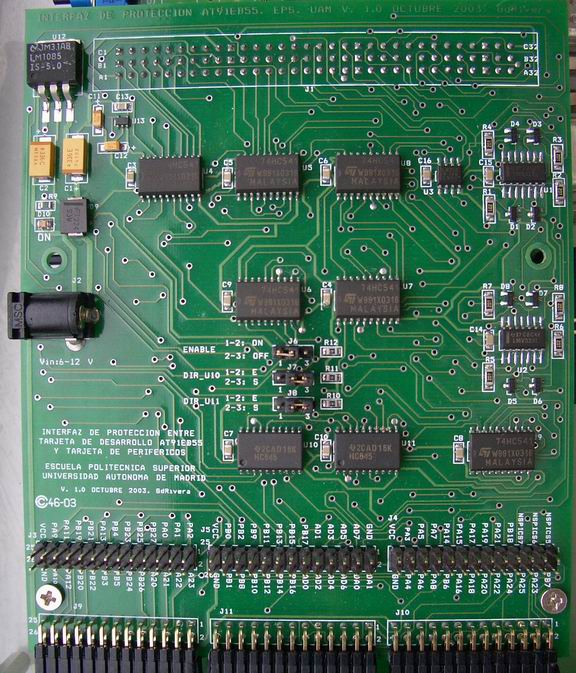

Tarjeta de Interfaz. Se conecta entre las dos anteriores y permite la protección del microcontrolador. Básicamente consta de unos buffers que aíslan las señales que entran y salen del microcontrolador.

En cuanto al software, en el laboratorio disponemos del Sistema de Desarrollo SDT 2.50 (ARM Software Development Toolkit 2.50 Manual de Referencia y Manual del Usuario). Dicho sistema está compuesto por un ensamblador, linker, depurador. También permite que las pruebas del programa desarrollado se pueden hacer sobre un emulador o bien sobre la propia tarjeta de evaluación.

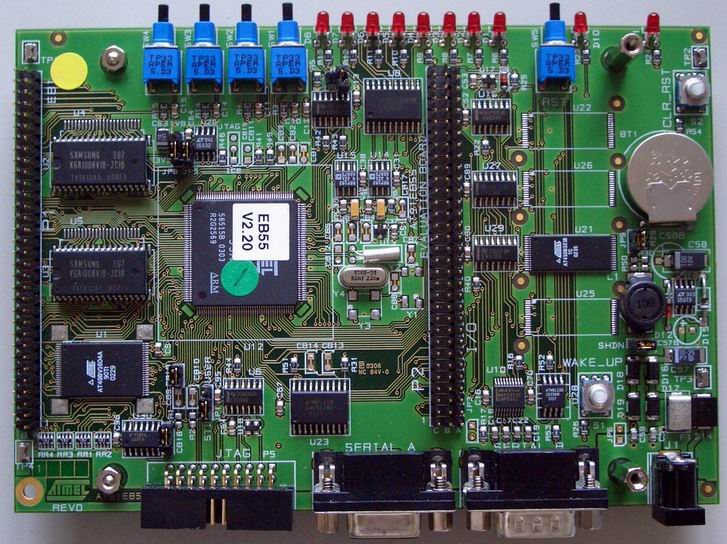

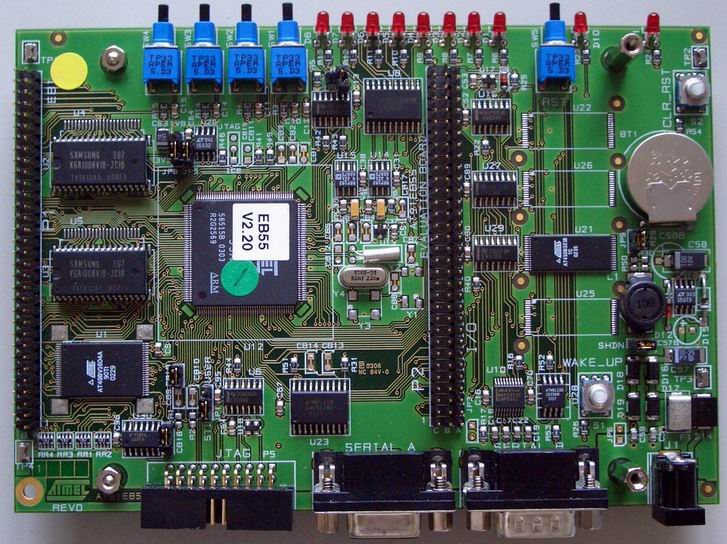

TARJETA DE EVALUACIÓN AT91EB55.

La tarjeta de evaluación es el modelo AT91EB55, de ATMEL. Está basada en el microcontrolador AT91M55800A, cuyo core es un ARM7 TDMI. La alimentación interna es entre 2,7 y 3,6 voltios, y entre 2,7 y 5,5 para las líneas de entrada/salida. Es totalmente estático y permite una frecuencia de reloj de hasta 33 MHz. Dispone de 8Kbytes de SRAM, bus de datos de 32 o 16 bits y de direcciones de 24 bits. Como periféricos integrados tiene 3 USARTs, 1 SPI, WatchDog, reloj de tiempo real, 6 temporizadores de 16 bits, un conversor analógico/digital de 10 bits con 8 canales y otro digital/analógico de 10 bits con dos canales y dos puertos de datos digitales de entrada/salida de 32 bits cada uno.

Las características principales de la tarjeta de evaluación son:

Gracias a los diferentes periféricos de los que se dispone, tanto en el propio microcontrolador como en la tarjeta de evaluación de ATMEL, sería posible desarrollar múltiples programas en los que se vería al funcionamiento del microprocesador como parte de un sistema. Pese a esto, se ha desarrollado una tarjeta, que se conecta al bus de expansión de entrada/salida, en la que se han conectado otros periféricos de propósito general que permitirán una mayor flexibilidad a la hora de diseñar otras prácticas. Esta tarjeta se describe en el siguiente punto.

Esta tarjeta consta de una serie de periféricos que se conectan al bus de entrada/salida de la Tarjeta de Evaluación descrita en el punto anterior. Dichos periféricos no están conectados entre sí, ni tampoco están conectados al bus de I/O. Sólo están conectados los pines de alimentación, el resto de líneas están disponibles a través de una serie de pines de wrapping de manera que el alumno los puede conectar donde él decida: bien entre ellos o bien a los pines que seleccione del bus de entrada/salida.

|

(Pinchar para ampliar) |

Pantalla de cristal líquido (LCD). Dispone de 2 líneas y 12 columnas. Los terminales del contraste están disponibles, de forma que se puede conectar un potenciómetro clásico o bien uno programable (en la placa descrita se encuentran ambos). El controlador del LCD es compatible con el estándar LSI HD44780. Breve descripción. Hoja resumen LCD. (Ver esquema)

Array de 4 displays de 7 segmentos, dispuestos en una configuración de ánodo común. (Ver esquema)

Teclado matricial de 16 teclas (16 pulsadores configurados como una matriz de 4x4) (Ver esquema)

4 pulsadores independientes. (Ver esquema)

4 interruptores. (Ver esquema)

8 diodos LED. (Ver esquema)

8 microinterruptores en formato DIL. (Ver esquema)

2 circuitos integrados MAX6817, de Maxim. Cada uno de ellos integra dos eliminadores de rebotes, útiles para filtrar las salidas de interruptores y pulsadores. (Ver esquema)

Un circuito integrado DS1806, de Dallas. Está compuesto por 6 potenciómetros de 64 posiciones, controlados por un bus de 3 hilos. (Ver esquema)

Dos circuitos integrados DS1804, de Dallas. Cada uno de ellos es un potenciómetro digital de 100 posiciones, no volátil. El control es por incremento/decremento a través de dos líneas. (Ver esquema)

Dos amplificadores operacionales, en una configuración de amplificador de ganancia variable. Se puede conectar una resistencia fija o cualquiera de los potenciómetros descritos anteriormente. (Ver esquema)

Dos señales analógicas, que pueden variar entre 0 y 2.5 voltios a través de sendos potenciómetros. (Ver esquema)

Dos drivers de potencia del tipo L293D, útiles para controlar motores. (Ver esquema)

Conexiones de VCC y GND, para selccionar entradas lógicas de 1 ó 0. (Ver esquema)

Una zona de wrapping, para incluir cualquier otro periférico. Esto permite al alumno el poder incluir cualquier otro elemento de manera que no le limite su diseño.

Como detalle adicional, mencionar que se han serigrafiado el nombre de cada una de las líneas, tanto en la cara de componentes como en la cara de soldadura, lo que facilita la conexión de los diferentes elementos. Así mismo se han duplicado los conectores que unen esta tarjeta con la de evaluación, de manera que se pueda conectar de forma sencilla un analizador lógico que permita el depurado del diseño.

TARJETA DE INTERFAZ (entre AT91EB55 y la de Periféricos).

Para evitar los posibles problemas que se pueden producir al realizar malas conexiones o cortocircuitos, también se ha diseñado una sencilla tarjeta que servirá de interfaz entre la tarjeta de evaluación, la que tiene el microcontrolador, y la tarjeta de periféricos. Básicamente se trata de hacer pasar cada línea por un buffer que aísle dichas señales, de forma que un exceso de tensión o una mala conexión no llegue a producir ninguna avería.

|

(Pulsar para ampliar) |

Está compuesta por los siguiente módulos:

Adaptadores de tensión analógica: Se utilizan para los conversores AD

y DA. En el caso de los AD toman como entrada la señal analógica del

exterior, con un circuito de protección, y como salida una señal entre 0 y

2.5 voltios, que es la tensión de referencia del conversor. En el caso del

conversor DA son simples seguidores de tensión.

Descripción de conexiones:

El hecho de conectar las líneas de entrada/salida a través de buffers para su protección implica que se impone la dirección de cada una de las líneas. La elección tomada se ha hecho en base a la función de cada pin cuando no estaba asociado al PIO. Esta tabla debe ser tenida en cuenta a la hora de asignar pines del micro a la conexión de los periféricos elegidos. La referencia de la dirección está tomada vista desde el microcontrolador.

|

PIN |

Función |

Dirección |

PIN |

Función |

Dirección |

PIN |

Función |

Dirección |

|

A1 |

GND |

-- |

B1 |

PB19 /

TCLK0 |

Entrada |

C1 |

GND |

-- |

|

A2 |

VCC3V3 |

-- |

B2 |

PB20 / TIOA0 |

E. Dig |

C2 |

VCC3V3 |

-- |

|

A3 |

PA9/IRQ0 |

E. Dig |

B3 |

PB21 / TIOB0 |

E. Dig |

C3 |

PB13 |

ES. Dig2 |

|

A4 |

PA10/IRQ1 |

E. Dig |

B4 |

PB22 / TCLK1 |

E. Dig |

C4 |

PB14 |

ES. Dig2 |

|

A5 |

GND |

-- |

B5 |

PB23 / TIOA1 |

S. Dig |

C5 |

PB15 |

ES. Dig2 |

|

A6 |

PA11/IRQ2 |

E. Dig |

B6 |

PB24 / TIOB1 |

S. Dig |

C6 |

PB16 |

ES. Dig2 |

|

A7 |

VCC3V3 |

-- |

B7 |

PB25 / TCLK2 |

E. Dig |

C7 |

PB17 |

ES. Dig2 |

|

A8 |

PA12/IRQ3 |

E. Dig |

B8 |

PB26 / TIOA2 |

S. Dig |

C8 |

VCC3V3 |

-- |

|

A9 |

GND |

-- |

B9 |

PB27 / TIOB2 |

S. Dig |

C9 |

GND |

-- |

|

A10 |

PA13/FIQ |

E. Dig |

B10 |

PA0 / TCLK3 |

E. Dig |

C10 |

A20 |

S. Dig |

|

A11 |

VCC3V3 |

-- |

B11 |

PA1 / TIOA3 |

E. Dig |

C11 |

A21 |

S. Dig |

|

A12 |

PB3/IRQ4 |

E. Dig |

B12 |

PA2 / TIOB3 |

E. Dig |

C12 |

A22 |

S. Dig |

|

A13 |

PB4/IRQ5 |

E. Dig |

B13 |

PA3 / TCLK4 |

E. Dig |

C13 |

A23 |

S. Dig |

|

A14 |

GND |

-- |

B14 |

PA4 /

TIOA4 |

S. Dig |

C14 |

GND |

-- |

|

A15 |

PB5/IRQ6 |

E. Dig |

B15 |

PA5 / TIOB4 |

S. Dig |

C15 |

DA0 |

S. Analog |

|

A16 |

PB0 |

ES. Dig1 |

B16 |

PA6 / TCLK5 |

E. Dig |

C16 |

GND |

-- |

|

A17 |

GND |

-- |

B17 |

PA7 / TIOA5 |

S. Dig |

C17 |

DA1 |

S. Analog |

|

A18 |

PB1 |

ES. Dig1 |

B18 |

PA8 / TIOB5 |

E. Dig |

C18 |

GND |

-- |

|

A19 |

PB2 |

ES. Dig1 |

B19 |

PA14 / SCK0 |

E. Dig |

C19 |

PB6/AD0TRIG |

E. Dig |

|

A20 |

PB8 |

ES. Dig1 |

B20 |

PA15 /

TXD0 |

NO Usar |

C20 |

GND |

-- |

|

A21 |

PB9 |

ES. Dig1 |

B21 |

PA16 / RXD0 |

NO Usar |

C21 |

AD0 |

E. Analog |

|

A22 |

VCC3V3 |

-- |

B22 |

PA17 / SCK1 |

S. Dig |

C22 |

AD1 |

E. Analog |

|

A23 |

PB10 |

ES. Dig1 |

B23 |

PA18/TXD1/NTRI |

S. Dig |

C23 |

AD2 |

E. Analog |

|

A24 |

PB11 |

ES. Dig1 |

B24 |

PA19 /

RXD1 |

E. Dig |

C24 |

AD3 |

E. Analog |

|

A25 |

PB12 |

ES. Dig1 |

B25 |

PA20 / SCK2 |

S. Dig |

C25 |

GND |

-- |

|

A26 |

PB18/BMS |

E. Dig |

B26 |

PA21 / TXD2 |

S. Dig |

C26 |

AD4 |

E. Analog |

|

A27 |

GND |

-- |

B27 |

PA22 / RXD2 |

E. Dig |

C27 |

AD5 |

E. Analog |

|

A28 |

NSPICS8 |

S. Dig |

B28 |

PA24 /

MISO |

E. Dig |

C28 |

AD6 |

E. Analog |

|

A29 |

NSPICS7 |

S. Dig |

B29 |

PA25 /

MOSI |

S. Dig |

C29 |

AD7 |

E. Analog |

|

A30 |

GND |

-- |

B30 |

PA23 / SPCK |

S. Dig |

C30 |

GND |

-- |

|

A31 |

VCC3V3 |

-- |

B31 |

NSPICS5 |

S. Dig |

C31 |

PB7/AD1TRIG |

E. Dig |

|

A32 |

GND |

-- |

B32 |

NSPICS6 |

S. Dig |

C32 |

GND |

-- |

E.Dig: Entrada digital (0-5 voltios)

S. Dig: Salida digital 0-5 voltios)

ES. Dig: Entrada ó Salida digital. Están agrupadas en dos bloques y la selección del sentido se realiza para todas las líneas del bloque.

ES. Dig1 :Jumper J8 1-2: Entradas

2-3: Salidas

ES. Dig2 :Jumper J7 1-2: Entradas

2-3: Salidas

E. Analog: Entrada analógica (de 0 a 2,5 voltios)

S. Analog: Salida analógica (de 0 a 2,5 voltios)

Existe un tercer jumper, J6, cuya misión es deshabilitar todos los buffers. EN la posición 1-2 están habilitados y en la 2-3 están deshabilitados.

Página editada y mantenida por Guillermo Glez. de Rivera