# UNIVERSIDAD AUTÓNOMA DE MADRID

# **ESCUELA POLITÉCNICA SUPERIOR**

# PROYECTO FIN DE CARRERA Ingeniería de Telecomunicación

Técnicas de Low-Power Design en FPGAs

Unai Montero Arratibel

Diciembre 2015

# Técnicas de Low-Power Design en FPGAs

**AUTOR: Unai Montero Arratibel**

**TUTOR: Juan Pablo Oliver Deferrari**

# **Digital System Lab**

Departamento de Tecnología Electrónica y de las Comunicaciones

**Escuela Politécnica Superior**

Universidad Autónoma de Madrid

Diciembre 2015

## Resumen

Este Proyecto de Fin de Carrera busca estudiar diferentes técnicas de diseño de circuitos digitales en FPGAs de forma empírica, de tal manera que puedan establecerse directrices que permitan implementar circuitos optimizando el consumo de los mismos. Para ello, se ha llevado a cabo el desarrollo de una serie de circuitos de prueba, de tal forma que un mismo circuito cuenta con varias implementaciones diferentes a nivel de diseño o bien el funcionamiento de una misma implementación ha sido estudiado en diferentes ambientes. La finalidad de este proceso es desarrollar un *benchmark* que permita establecer de forma experimental cómo afectan las diferentes variables que definen y rodean a un circuito al consumo del mismo.

## Palabras clave

FPGA, circuito, digital, transición, lógica, aritmética, función, potencia, disipación, modelo, temperatura, voltaje, corriente, capacidad, diseño, *low-power*, optimización, reducción, medida, parásita, *glitch, Xilinx*

## **Abstract**

This Project aims to study different techniques of digital circuit design in FPGAs empirically, so that some guidelines to implement circuits can be defined to optimize their power dissipated. In order to achieve this goal, a number of test circuits has been developed, having implemented each one of them in several ways or keeping the same implementation but varying the environment surrounding the circuit. The purpose of this process is to develop a benchmark thats allows establishing experimentally how the different variables that define and surround a circuit affect their power dissipated.

# **Key words**

FPGA, circuit, digital, transition, logical, arithmetic, function, power, dissipation, model, temperature, voltage, current, capacity, design, low-power, optimization, reduction, measure, parasitic, glitch, *Xilinx*

# **Agradecimientos**

En primer lugar me gustaría agradecer a mi familia todo el apoyo que me han brindado de manera constante a lo largo de todos estos años. Quiero darles las gracias por haberme inculcado los valores y dado la educación que he necesitado para llegar hasta este punto y que sin duda me servirán de guía en el futuro. A mi madre, por compartir conmigo tanto los disgustos como las alegrías durante todo este tiempo, por empujar junto a mí desde el principio hasta el final. A mi padre por confiar en mí incluso en los momentos más duros, por su trabajo abnegado y su entrega. A mi hermano por su apoyo incondicional, por su capacidad de arrancar una risa cuando más se necesita.

Gracias a todos los compañeros con los que he compartido el camino y que de uno u otro modo me han ayudado a llegar hasta el final, en particular a Pablo y a Eugenio. Me siento muy afortunado de haberme cruzado con vosotros por el camino.

Gracias tanto a mi tutor, Juan Pablo Oliver, como a Eduardo Boemo, por darme la oportunidad de desarrollar este proyecto, por su buena disposición a echarme una mano siempre que lo he necesitado. Sin vuestra guía no habría sido posible.

Gracias a todos los profesores que me he cruzado a lo largo de todos estos años, tanto en el colegio como en la universidad. Gracias por haber aportado vuestro granito de arena.

Gracias a Marta, porque teniéndote cerca todo resulta más fácil.

Muchas gracias a todos.

**Unai Montero Arratibel**

Diciembre 2015

# Índice de contenidos

| Resur  | men                                                       | 5  |

|--------|-----------------------------------------------------------|----|

| Palab  | ras clave                                                 | 5  |

| Abstr  | act                                                       | 6  |

| Key w  | vords                                                     | 6  |

| Capít  | ulo 1                                                     | 19 |

| 1.1    | Motivación                                                | 19 |

| 1.2    | Objetivos                                                 | 20 |

| 1.3    | Metodología                                               | 20 |

| 1.4    | Estructura                                                | 21 |

| 1.5    | Siglas y acrónimos                                        | 21 |

| Capít  | ulo 2                                                     | 23 |

| 2.1 Pa | anorámica                                                 | 23 |

| 2.2 D  | elimitación del espacio de trabajo                        | 23 |

| 2.2    | 1 Fuentes de consumo                                      | 23 |

| 2.2    | 2 Voltaje                                                 | 24 |

| 2.2    | 3 Capacitancia                                            | 25 |

| 2.2    | .4 Actividad de datos dentro del circuito                 | 25 |

| 2      | 2.2.4.1 Patrón de la entrada de datos                     | 26 |

| 2      | 2.2.4.2 Modelo de retardo                                 | 30 |

| 2      | 2.2.4.3 Funciones lógicas                                 | 32 |

| 2      | 2.2.4.4 Lógica estática vs. lógica dinámica               | 35 |

| 2      | 2.2.4.5 Estructura del circuito                           | 35 |

| 2.3 Té | écnicas de estimación de consumo en circuitos             | 36 |

| 2.3    | .1 Técnicas de simulación                                 | 36 |

| 2      | 2.3.1.1 Simulación directa                                | 36 |

| 2      | 2.3.1.2 Simulación jerarquizada                           | 36 |

| 2      | 2.3.1.3 Muestreo estadístico                              | 37 |

| 2.3    | .2 Técnicas alternativas a la simulación                  | 37 |

| 2      | 2.3.2.1 Estimación a nivel de comportamiento del circuito | 37 |

| 2      | 2.3.2.2 Estimación a nivel lógico                         | 38 |

| 2.4 Te | écnicas de reducción de consumo                           | 40 |

| 2.4    | .1 Escalado del voltaje de alimentación                   | 41 |

| 2.4    | .2 Minimización de la capacitancia                        | 41 |

| 2.4    | .3 Gestión de potencia y técnicas de diseño               | 43 |

| Capít  | ulo 3                                                     | 47 |

| 3.1 AVNET Xilinx Spartan-6 FPGA LX16 Evaluation Kit                                                                                          | 47            |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 3.1.1 Placa AVNET                                                                                                                            | 47            |

| 3.1.2 FPGA Xilinx Spartan-6                                                                                                                  | 49            |

| 3.1.2.1 FPGAs de la familia <i>Spartan-6</i>                                                                                                 | 49            |

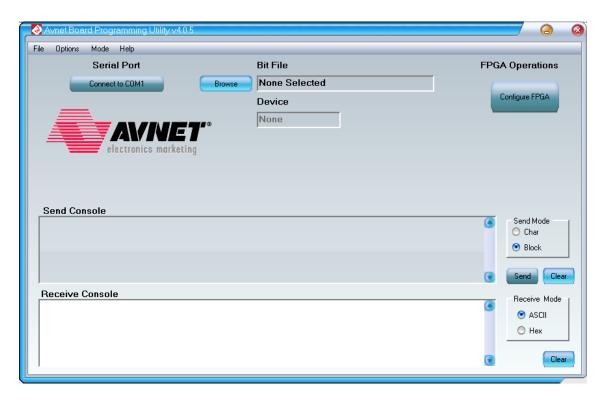

| 3.1.3 Herramienta de medición de consumo de <i>AvProg</i>                                                                                    | 51            |

| 3.2 Estufa de secado <i>Selecta Digitheat</i>                                                                                                | 53            |

| 3.3 Xilinx ISE Design Suite 14.6                                                                                                             | 55            |

| Capítulo 4                                                                                                                                   | 57            |

| 4.1 Metodología y desarrollo                                                                                                                 | 57            |

| 4.2 Listado de circuitos que componen el <i>benchmark</i>                                                                                    | 59            |

| 4.2.1 Diseños relativos a la variación del número de etapas de pipeline                                                                      | 59            |

| 4.2.2 Diseños relativos a la variación de la frecuencia de funcionamiento del circuito                                                       | 60            |

| 4.2.3 Diseños relativos a la variación del algoritmo utilizado dentro del circuito                                                           | 60            |

| 4.2.4 Diseños relativos a la variación de la temperatura de la FPGA                                                                          | 60            |

| 4.2.5 Relación entre los diferentes parámetros                                                                                               | 60            |

| 4.2.6 Consideraciones relativas al tamaño de los circuitos                                                                                   | 61            |

| 4.2.7 Multiplicadores vs. LUTs                                                                                                               | 61            |

| 4.3 Desarrollo de los procesos de medición y resultados obtenidos                                                                            | 61            |

| 4.3.1 Variación en el número de etapas de pipeline                                                                                           | 61            |

| 4.3.1.1 La segmentación de circuitos digitales o pipelining                                                                                  | 61            |

| 4.3.1.2 Desarrollo de las mediciones relativas a la variación del número de etapas de p                                                      | ipeline<br>61 |

| 4.3.1.3 Presentación de resultados de las mediciones relativas a la variación del númer etapas de <i>pipeline</i>                            | o de<br>62    |

| 4.3.2 Variación de la frecuencia de funcionamiento del circuito                                                                              | 68            |

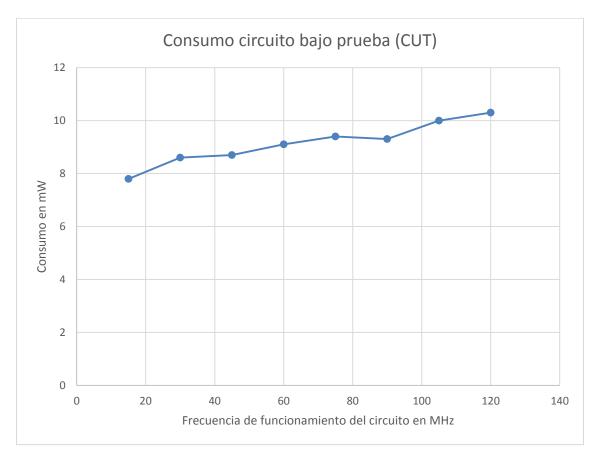

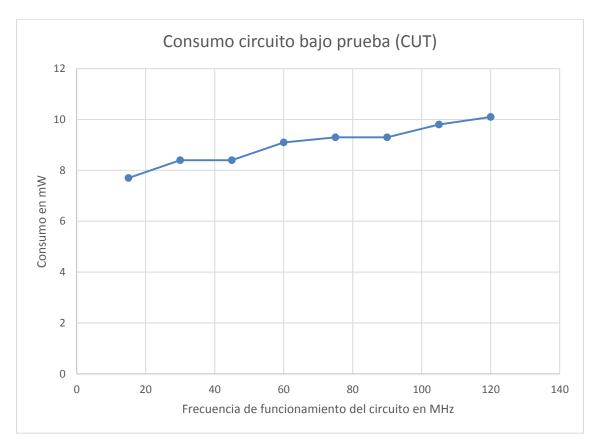

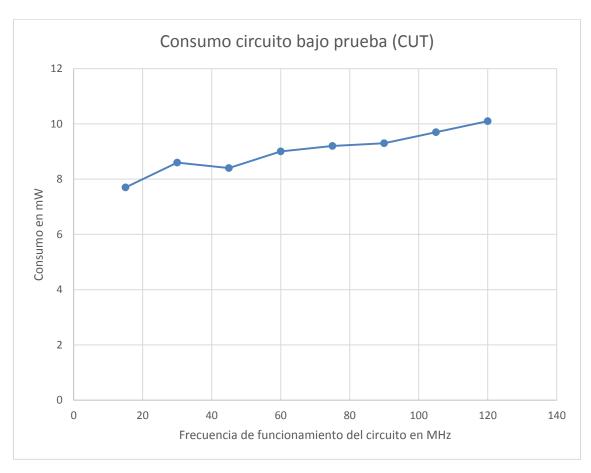

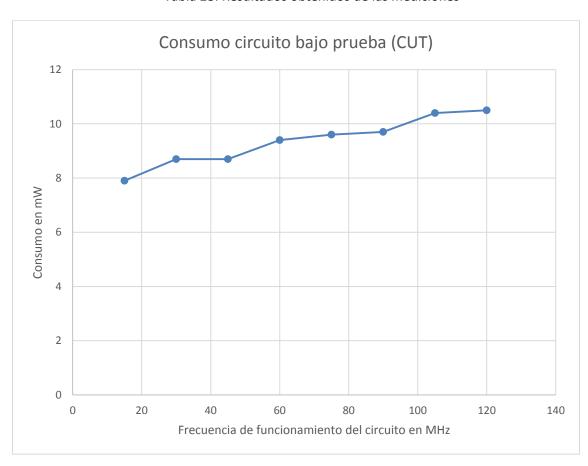

| 4.3.2.1 Presentación de resultados de las mediciones relativas a la variación de la frecu<br>de funcionamiento del circuito: multiplicadores | uencia<br>69  |

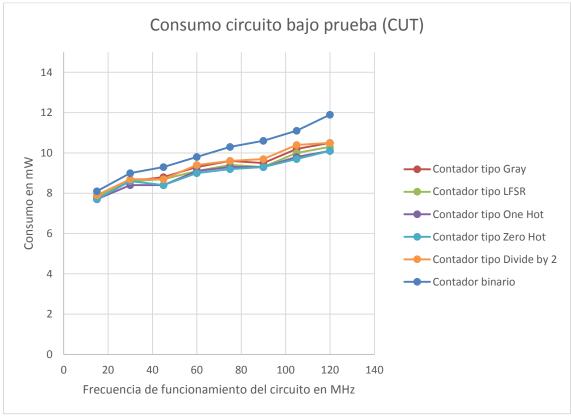

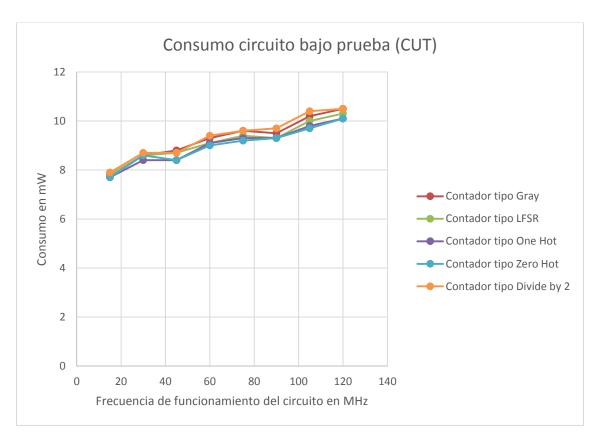

| 4.3.2.2 Presentación de resultados de las mediciones relativas a la variación de la frecu<br>de funcionamiento del circuito: contadores      | uencia<br>77  |

| 4.3.3 Variación del algoritmo utilizado dentro del circuito                                                                                  | 83            |

| 4.3.3.1 Presentación de resultados de las mediciones relativas a la variación del algorit utilizado dentro del circuito                      | mo<br>85      |

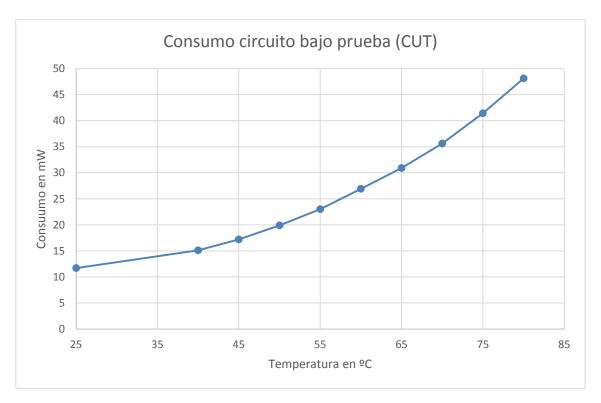

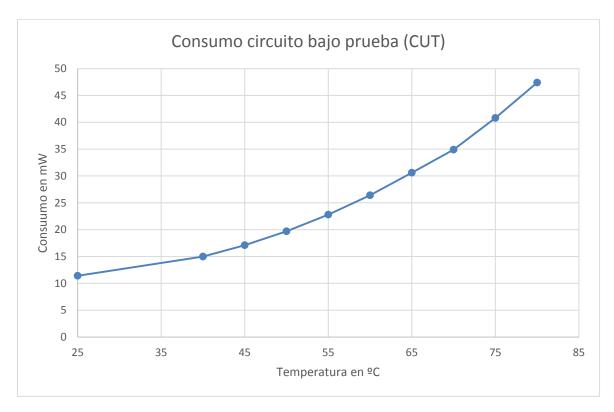

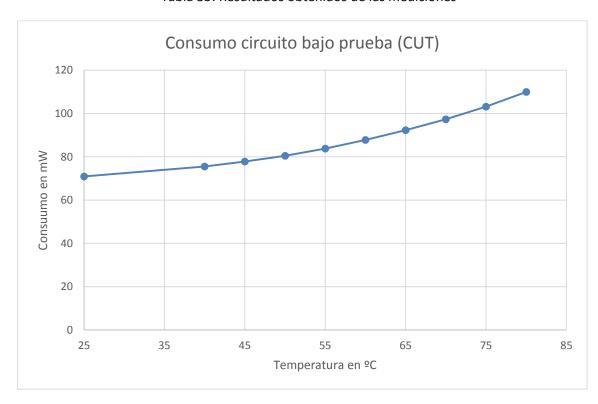

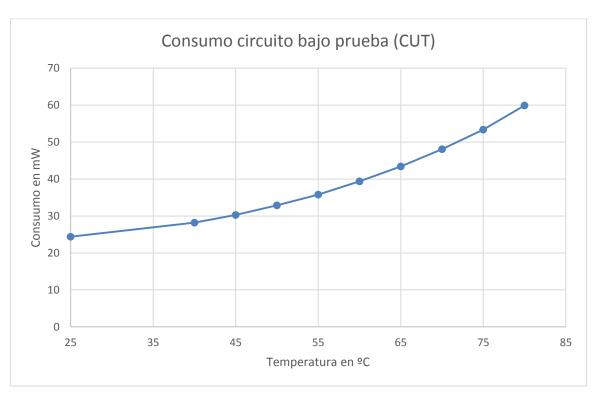

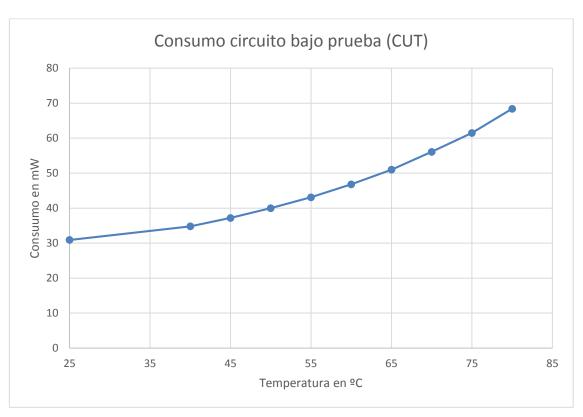

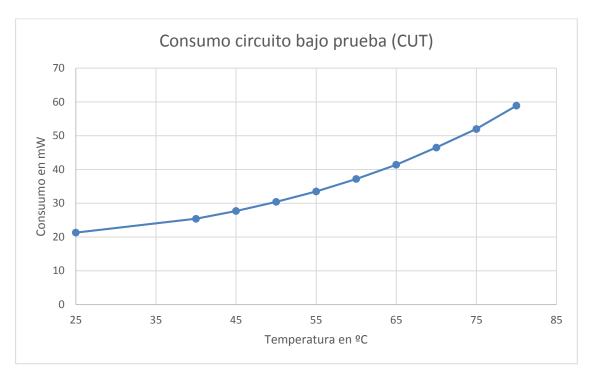

| 4.3.4 Variación de la temperatura de la FPGA                                                                                                 | 87            |

| 4.3.4.1 Metodología del proceso de medición                                                                                                  | 87            |

| 4.3.4.2 Presentación de resultados de las mediciones relativas a la variación de la                                                          |               |

| temperatura de la FPGA                                                                                                                       | 88            |

| Capítulo 5                                                                                                                                   | 102           |

| 5.1 Comportamiento del consumo con respecto al número de etapas de pipeline                 | 102          |

|---------------------------------------------------------------------------------------------|--------------|

| 5.2 Comportamiento del consumo con respecto a la frecuencia de funcionamiento de los circ   | uitos<br>102 |

| 5.3 Comportamiento del consumo con respecto al algoritmo utilizado en el circuito           | 103          |

| 5.4 Comportamiento del consumo con respecto a la temperatura a la que se encuentra el circ  | cuito<br>103 |

| 5.5 Búsqueda de resultados vs. cálculo de resultados                                        | 103          |

| 5.5 Líneas de trabajo futuro                                                                | 104          |

| Referencias                                                                                 | 105          |

| Anexo I: Listado de circuitos y mediciones                                                  | 106          |

| Listado de diseños relativos a la variación del número de etapas de pipeline                | 106          |

| Listado de diseños relativos a la variación de la frecuencia de funcionamiento del circuito | 107          |

| Listado de diseños relativos a la variación del algoritmo utilizado dentro del circuito     | 110          |

| Listado de diseños relativos a la variación de la temperatura de la FPGA                    | 111          |

| Anexo II: Presupuesto                                                                       | 116          |

| Anexo III: Pliego de condiciones                                                            | 117          |

# Índice de figuras

| Fig.1: Contraposición modelo real-ideal                            | 31 |

|--------------------------------------------------------------------|----|

| Fig. 2: Contraposición modelo booleano-forma de onda               | 39 |

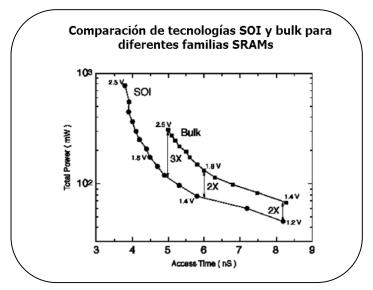

| Fig.3: Comparación SOI-bulk en SRAMs                               | 42 |

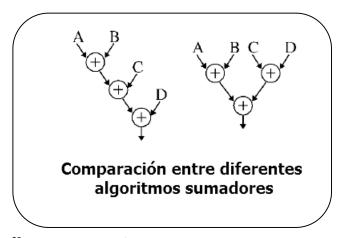

| Fig. 4: Comparación algoritmos sumadores                           | 43 |

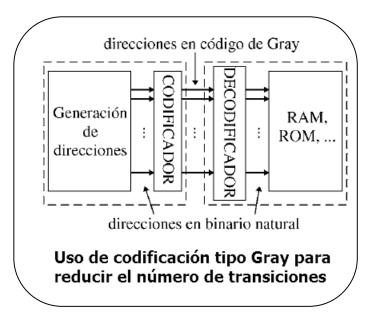

| Fig.5: Codificación Gray para reducir transiciones                 | 44 |

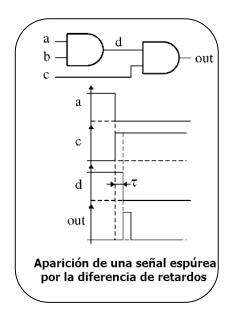

| Fig.6: Señal espúrea por retardo                                   | 44 |

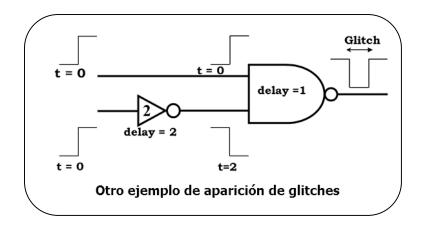

| Fig.7: Aparición de <i>glitches</i>                                | 45 |

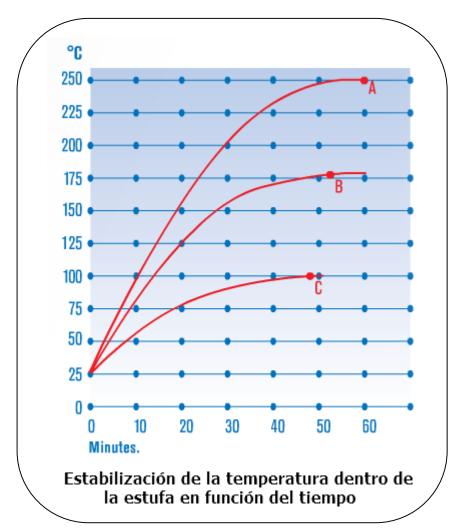

| Fig.8: Estabilización de la temperatura dentro de la estufa        | 55 |

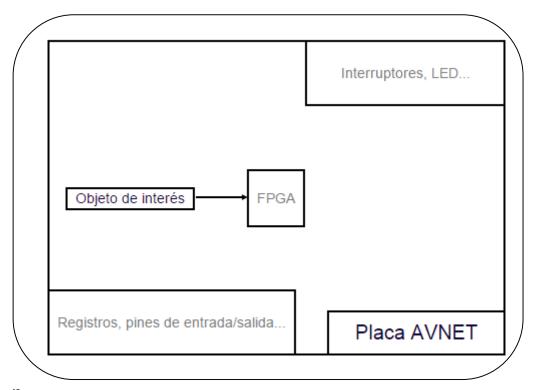

| Fig.9: Identificación del objeto de interés: FPGA                  | 57 |

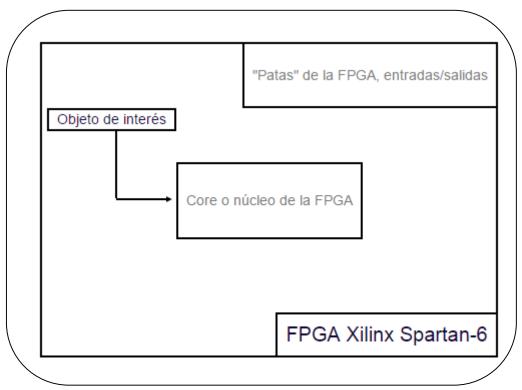

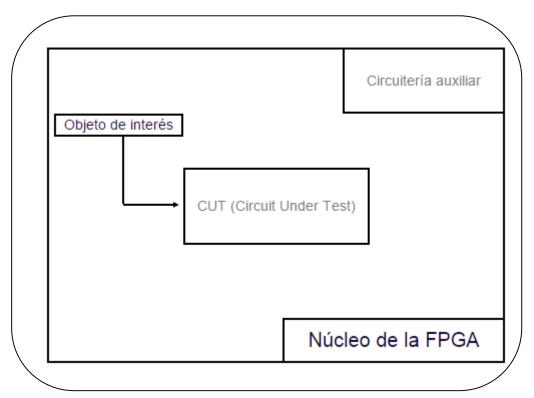

| Fig. 10: Identificación del objeto de interés: núcleo de la FPGA   | 58 |

| Fig.11: Identificación del objeto de interés: circuito bajo prueba | 59 |

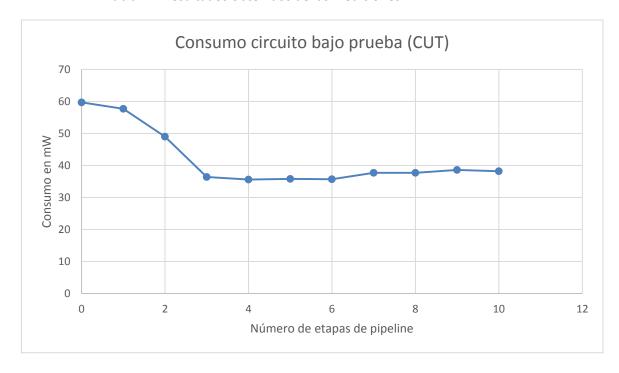

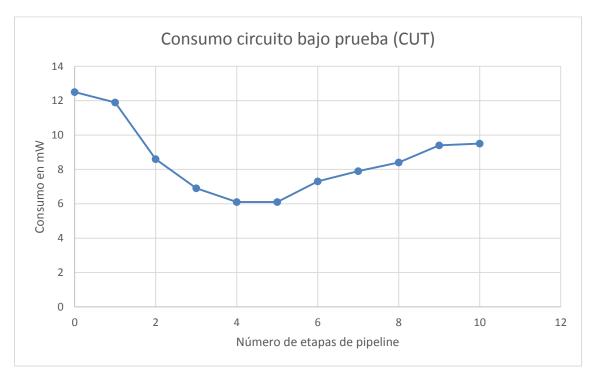

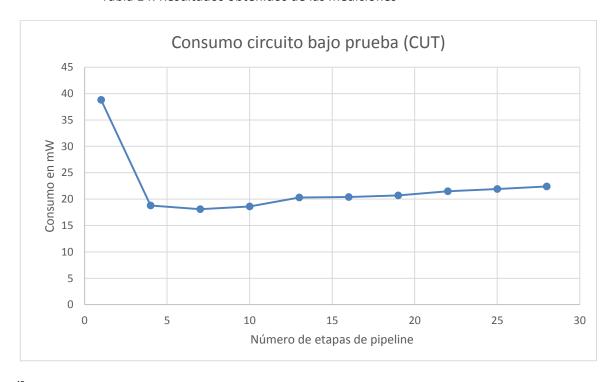

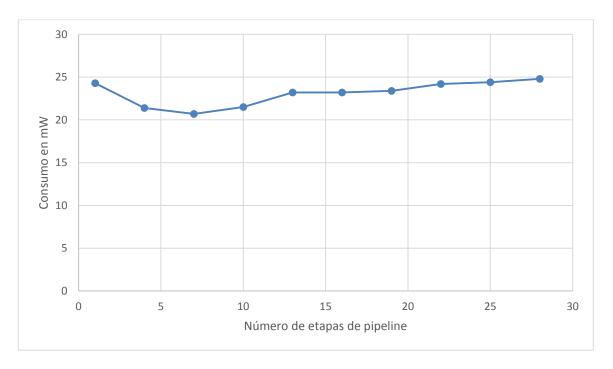

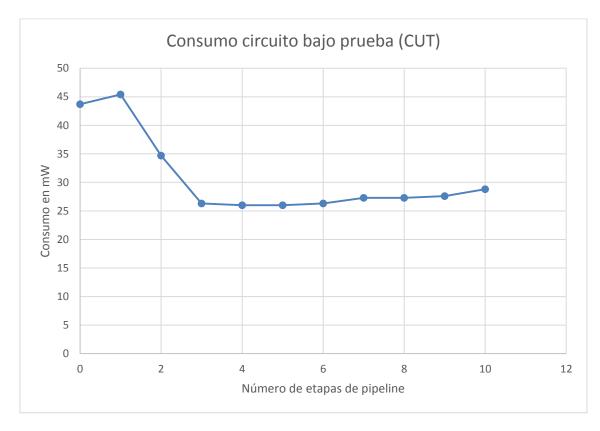

| Fig.12: Representación gráfica del resultado de las mediciones     | 62 |

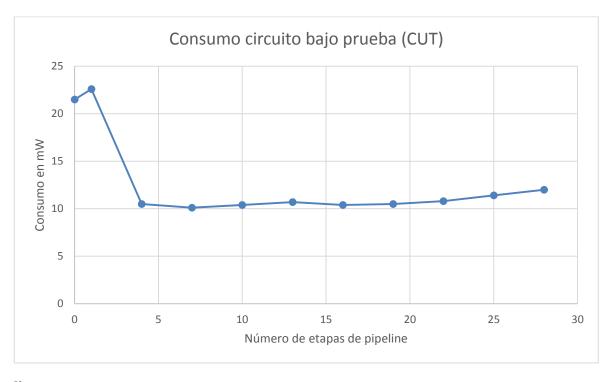

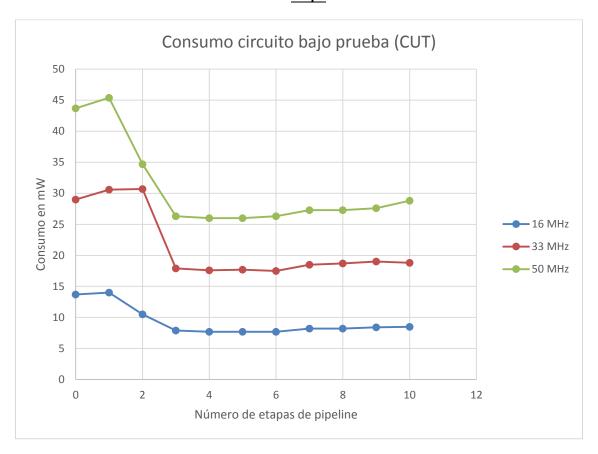

| Fig. 13: Representación gráfica del resultado de las mediciones    | 63 |

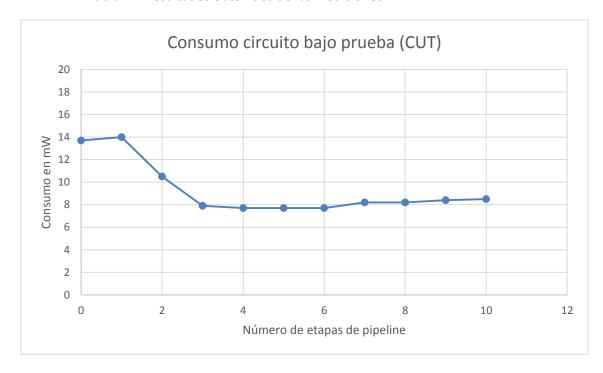

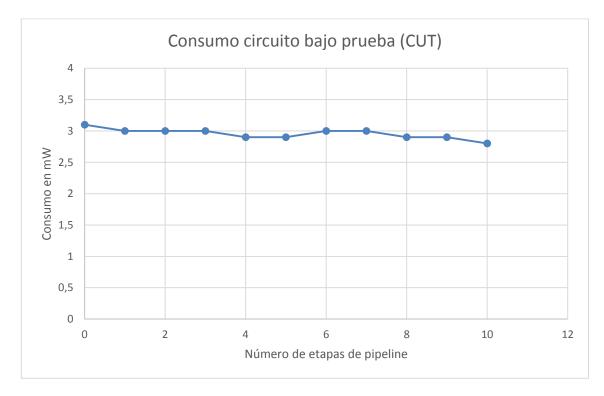

| Fig.14: Representación gráfica del resultado de las mediciones     | 65 |

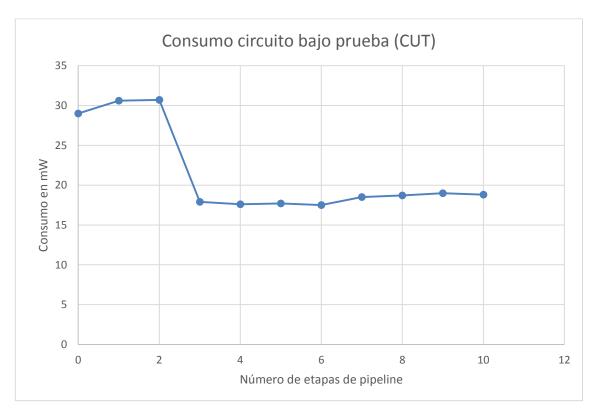

| Fig. 15: Representación gráfica del resultado de las mediciones    | 66 |

| Fig.16: Representación gráfica del resultado de las mediciones     | 67 |

| Fig.17: Representación gráfica del resultado de las mediciones     | 69 |

| Fig. 18: Representación gráfica del resultado de las mediciones    | 70 |

| Fig. 19: Representación gráfica del resultado de las mediciones    | 71 |

| Fig. 20: Representación gráfica del resultado de las mediciones    | 72 |

| Fig.21: Representación gráfica del resultado de las mediciones     | 73 |

| Fig. 22: Representación gráfica del resultado de las mediciones    | 74 |

| Fig. 23: Representación gráfica del resultado de las mediciones    | 75 |

| Fig.24: Representación gráfica del resultado de las mediciones     | 76 |

| Fig. 25: Representación gráfica del resultado de las mediciones    | 77 |

| Fig. 26: Representación gráfica del resultado de las mediciones    | 78 |

| Fig. 27: Representación gráfica del resultado de las mediciones    | 79 |

| Fig. 28: Representación gráfica del resultado de las mediciones    | 80 |

| Fig. 29: Representación gráfica del resultado de las mediciones    | 81 |

| Fig.30: Representación gráfica del resultado de las mediciones     | 82 |

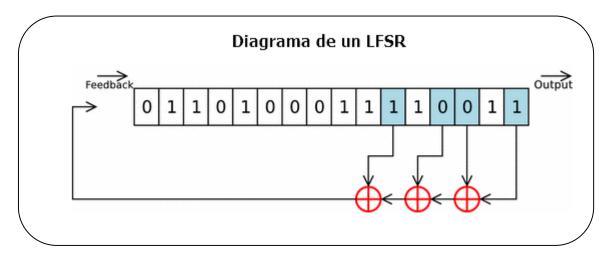

| Fig.31: Diagrama de un contador LFSR                               | 83 |

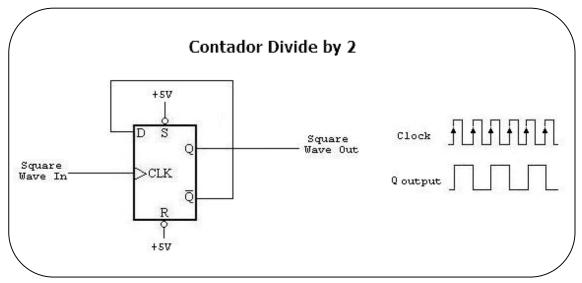

| Fig.32: Diagrama de un contador Divide by 2                        | 84 |

| Fig.33: Representación gráfica del resultado de las mediciones     | 85 |

| Fig.34: Representación gráfica del resultado de las mediciones     | 86 |

|                                                                    |    |

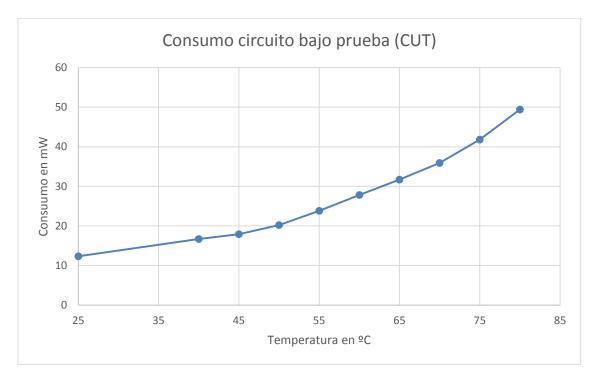

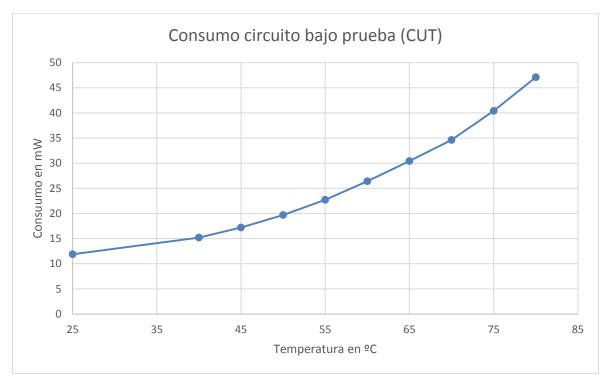

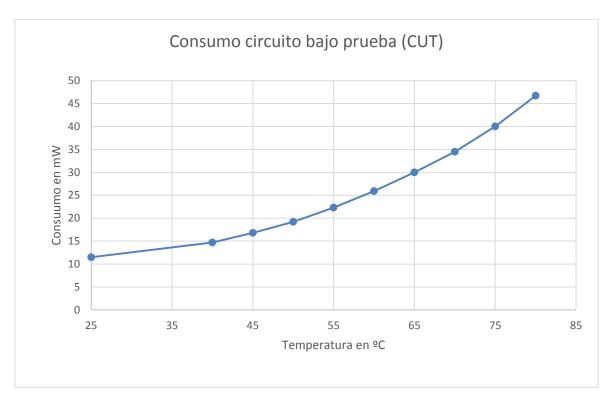

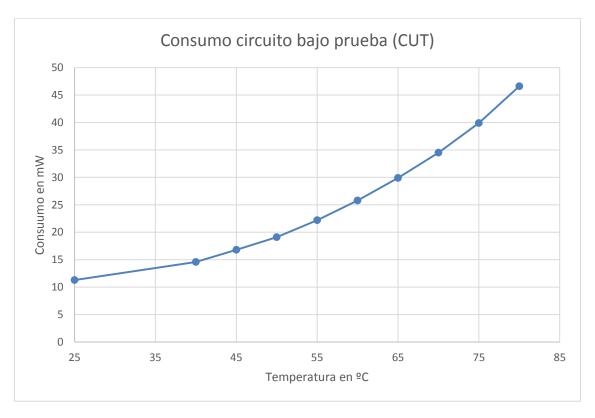

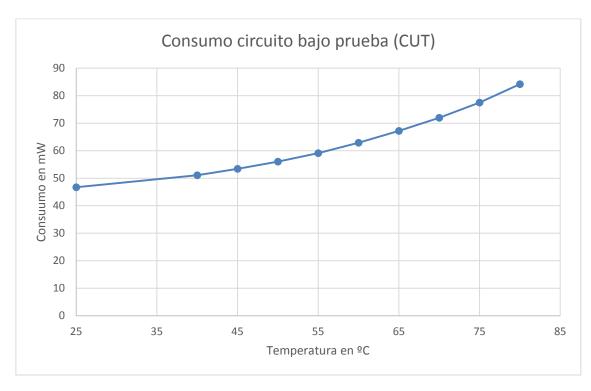

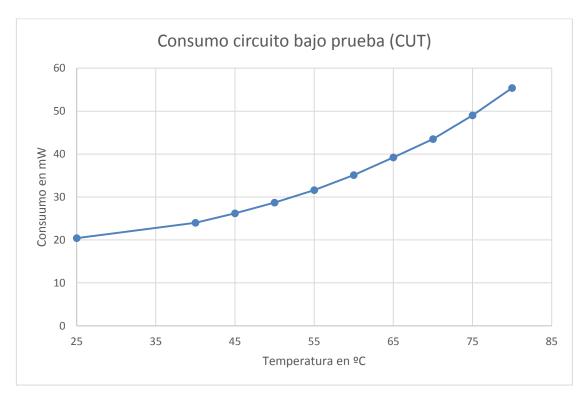

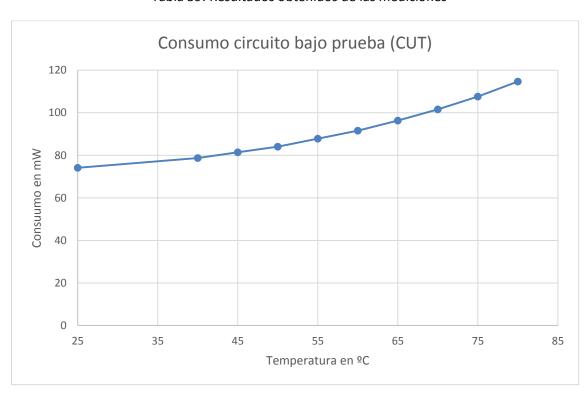

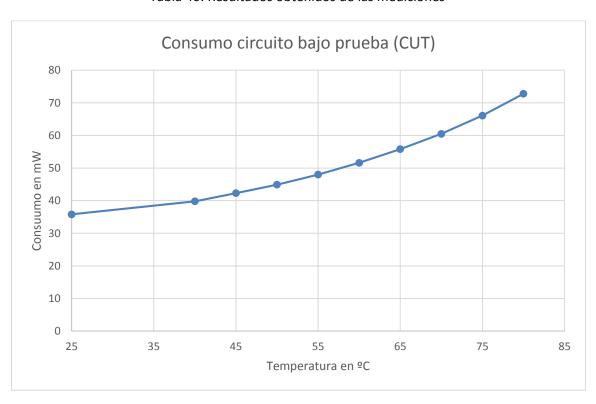

| Fig.35: Representación gráfica del resultado de las mediciones | 88  |

|----------------------------------------------------------------|-----|

| Fig.36: Representación gráfica del resultado de las mediciones | 89  |

| Fig.37: Representación gráfica del resultado de las mediciones | 90  |

| Fig.38: Representación gráfica del resultado de las mediciones | 91  |

| Fig.39: Representación gráfica del resultado de las mediciones | 92  |

| Fig.40: Representación gráfica del resultado de las mediciones | 93  |

| Fig.41: Representación gráfica del resultado de las mediciones | 94  |

| Fig.42: Representación gráfica del resultado de las mediciones | 95  |

| Fig.43: Representación gráfica del resultado de las mediciones | 96  |

| Fig.44: Representación gráfica del resultado de las mediciones | 97  |

| Fig.45: Representación gráfica del resultado de las mediciones | 98  |

| Fig.46: Representación gráfica del resultado de las mediciones | 99  |

| Fig.47: Representación gráfica del resultado de las mediciones | 100 |

| Fig.48: Representación gráfica del resultado de las mediciones | 101 |

# Índice de tablas

| Tabla 1: Tabla de verdad OR                                       | 26 |

|-------------------------------------------------------------------|----|

| Tabla 2: Transiciones puerta OR                                   | 27 |

| Tabla 3: Transiciones puerta OR                                   | 28 |

| Tabla 4: Transiciones puerta OR                                   | 28 |

| Tabla 5: Transiciones puerta OR                                   | 29 |

| Tabla 6: Tabla de verdad AND                                      | 32 |

| Tabla 7: Tabla de verdad XOR                                      | 32 |

| Tabla 8: Transiciones puerta AND                                  | 33 |

| Tabla 9: Transiciones puerta XOR                                  | 34 |

| Tabla 10: Especificaciones FPGA Xilinx Spartan-6 XC6SLX16-CSG324C | 51 |

| Tabla 11: Características familia Spartan                         | 52 |

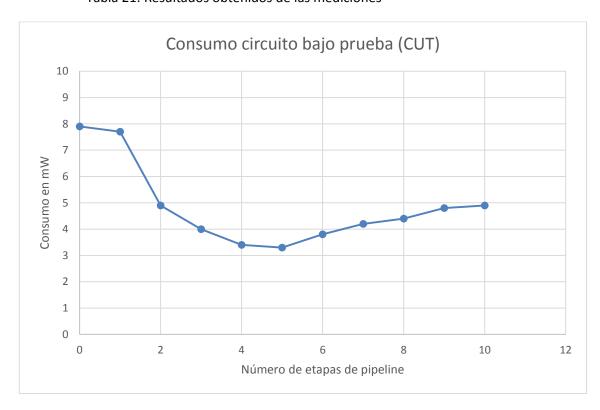

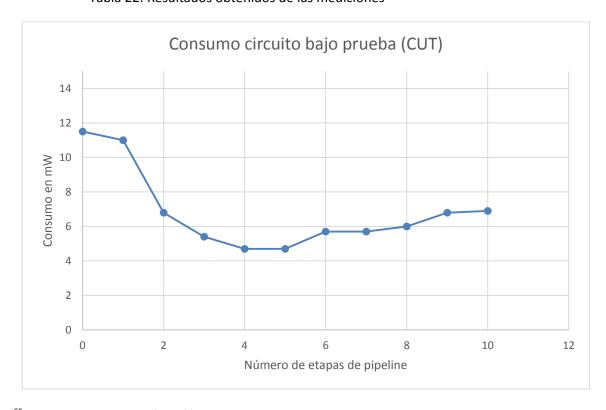

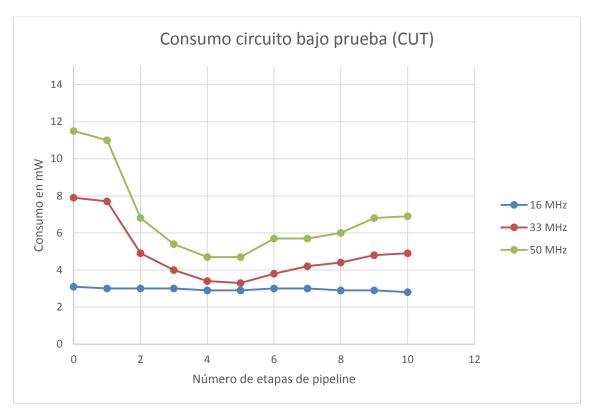

| Tabla 12: Resultados obtenidos de las mediciones                  | 63 |

| Tabla 13: Resultados obtenidos de las mediciones                  | 64 |

| Tabla 14: Resultados obtenidos de las mediciones                  | 66 |

| Tabla 15: Resultados obtenidos de las mediciones                  | 67 |

| Tabla 16: Resultados obtenidos de las mediciones                  | 68 |

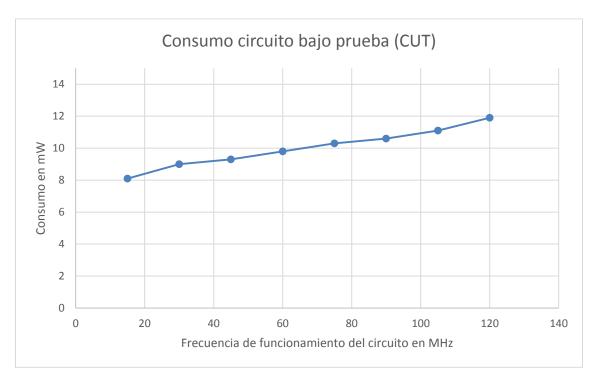

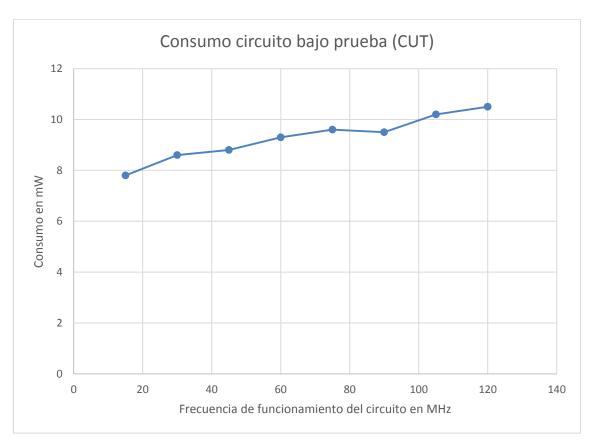

| Tabla 17: Resultados obtenidos de las mediciones                  | 70 |

| Tabla 18: Resultados obtenidos de las mediciones                  | 71 |

| Tabla 19: Resultados obtenidos de las mediciones                  | 72 |

| Tabla 20: Resultados obtenidos de las mediciones                  | 74 |

| Tabla 21: Resultados obtenidos de las mediciones                  | 75 |

| Tabla 22: Resultados obtenidos de las mediciones                  | 76 |

| Tabla 23: Resultados obtenidos de las mediciones                  | 78 |

| Tabla 24: Resultados obtenidos de las mediciones                  | 79 |

| Tabla 25: Resultados obtenidos de las mediciones                  | 80 |

| Tabla 26: Resultados obtenidos de las mediciones                  | 81 |

| Tabla 27: Resultados obtenidos de las mediciones                  | 82 |

| Tabla 28: Resultados obtenidos de las mediciones                  | 83 |

| Tabla 29: Resultados obtenidos de las mediciones                  | 89 |

| Tabla 30: Resultados obtenidos de las mediciones                  | 90 |

| Tabla 31: Resultados obtenidos de las mediciones                  | 91 |

| Tabla 32: Resultados obtenidos de las mediciones                  | 92 |

| Tabla 33: Resultados obtenidos de las mediciones                  | 93 |

| Tabla 34: Resultados obtenidos de las mediciones                  | 94 |

| Tabla 35: Resultados obtenidos de las mediciones | 95  |

|--------------------------------------------------|-----|

| Tabla 36: Resultados obtenidos de las mediciones | 96  |

| Tabla 37: Resultados obtenidos de las mediciones | 97  |

| Tabla 38: Resultados obtenidos de las mediciones | 98  |

| Tabla 39: Resultados obtenidos de las mediciones | 99  |

| Tabla 40: Resultados obtenidos de las mediciones | 100 |

| Tabla 41: Resultados obtenidos de las mediciones | 101 |

| Tabla 42: Resultados obtenidos de las mediciones | 102 |

# Índice de ecuaciones

| Ec.1: Consumo de un circuito                                      | 23 |

|-------------------------------------------------------------------|----|

| Ec.2: Probabilidad de transición a la salida de un circuito       | 27 |

| Ec.3: Probabilidad de transición a la salida de un circuito       | 28 |

| Ec.4: Probabilidad de transición a la salida de un circuito       | 29 |

| Ec.5: Probabilidad de transición a la salida de un circuito       | 29 |

| Ec.6: Probabilidad de transición a la salida de un circuito       | 33 |

| Ec.7: Probabilidad de transición a la salida de un circuito       | 34 |

| Ec.8: Probabilidad de transición a la salida de un circuito       | 34 |

| Ec.9: Número de muestras requerido para la estimación del consumo | 37 |

| Ec.10: Factor de actividad dentro de un circuito                  | 38 |

| Ec.11: Estimación de la actividad dentro de un circuito           | 39 |

# Índice de fotografías

| Fot.1: Placa AVNET utilizada para el desarrollo del estudio                               | 49 |

|-------------------------------------------------------------------------------------------|----|

| Fot.2: FPGA Xilinx Spartan-6 utilizada para el desarrollo del estudio                     | 51 |

| Fot.3: Interfaz gráfica AvProg – Conexión, configuración y carga de los diseños           | 53 |

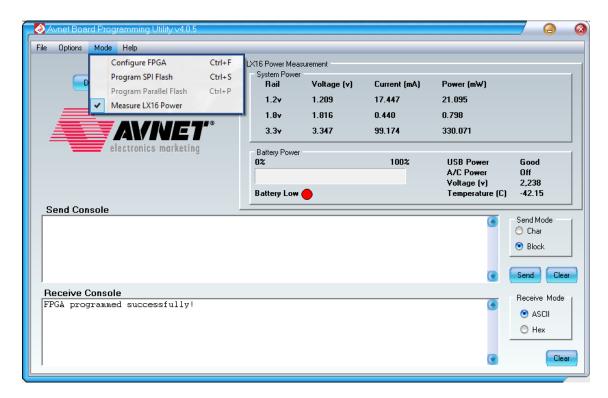

| Fot.4: Interfaz gráfica AvProg – Lanzamiento de la monitorización de consumo              | 54 |

| Fot.5: Estufa de secado y esterilización <i>Selecta Digitheat</i> utilizada en el estudio | 55 |

# Capítulo 1 - Introducción

## 1.1 Motivación

A día de hoy, la electrónica está presente en innumerables escenarios, todo cuanto rodea al ser humano actual tiene alguna relación directa o indirecta con ella. Es por ello que resulta de vital importancia la maximización de la eficiencia a la hora de utilizarla. En estas circunstancias, aparece la necesidad de obtener un bajo consumo sin sacrificar por ello un alto rendimiento. A raíz de este punto, surge la dicotomía entre ambas cualidades y la búsqueda por encontrar una solución de compromiso entre ellas.

En un pasado aún no muy lejano, las preocupaciones principales a la hora de diseñar circuitos de toda índole residían en reducir el área resultante, optimizar el rendimiento, minimizar los costes y maximizar la velocidad de operación. Este hecho conduce a preguntarse en qué momento y por qué motivo cobra una importancia clave la reducción del consumo. La respuesta a esta cuestión se halla en la naturaleza portátil de muchos dispositivos utilizados en el presente. Su carácter ubicuo fuerza a los mismos a hacer uso de una batería, lo cual no hace sino aumentar el objeto de este estudio. Sin embargo, esto no implica que este problema se limite únicamente a este tipo de aparatos, puesto que los que poseen una naturaleza fija que necesita de un suministro de energía continuo son objeto de esta misma cuestión. En medio de este escenario se encuentra la piedra angular de este estudio, la FPGA.

Los circuitos digitales integrados están compuestos por puertas lógicas que ofrecen un resultado a su salida en función del valor que se encuentre en sus entradas. De esta forma, las funciones que pueda llevar a cabo un circuito integrado vendrán determinadas por el número de puertas, su tipo y las interconexiones que existan entre ellas.

Una FPGA (*Field Programable Gate Array*) es un circuito integrado "en blanco", no tiene funciones definidas. Posee un número de puertas lógicas en su interior, sin configurar ni conectar entre sí. Es el usuario el que debe encargarse de configurar e interconectar esa lógica interna para definir la función o funciones que tendrá esa FPGA. Además, las FPGAs pueden ser reprogramadas tantas veces como se desee, por lo que las posibilidades que ofrecen son mayores si cabe, desde la creación de nuevos circuitos hasta la reproducción de otros ya existentes, siempre que la FPGA sea lo suficientemente grande y posea un número de puertas suficiente.

La programación de la FPGA difiere de la que se lleva a cabo en otros dispositivos como pueden ser DSPs o microcontroladores. Una FPGA cuenta con celdas que son configuradas con una función específica, ya sea como memoria, función lógica, multiplexor, etc. En el proceso de programación, se describe el hardware que tiene la FPGA, por lo que es el programador el que deberá definir la función lógica que llevará a cabo cada CLB (*Configurable Logic Block*) así como cada IOB (*Input/Output Block*). Este proceso de diseño y posterior carga puede llevarse a cabo mediante la utilización de esquemáticos, sin embargo, lo más común es usar lenguajes de programación conocidos como HDL (*Hardware Description Language*). Los más utilizados a día de hoy son *Verilog* y *VHDL*, siendo este último el que se ha utilizado para el desarrollo de los circuitos empleados en este trabajo.

Según lo expuesto hasta este momento, las grandes ventajas que presentan las FPGAs podrían resumirse en:

- Alto rendimiento

- Facilidad de stock

- Tolerancia a errores de diseño gracias a la posibilidad de ser reprogramadas

- Fiabilidad

- Precios asequibles

- Gran flexibilidad gracias a su carácter reprogramable

Todo lo expuesto anteriormente lleva a particularizar la optimización de consumo al caso de las FPGAs. Además, su flexibilidad y la capacidad de ser programadas tantas veces como se desee las hacen idóneas para la medición de una infinidad de circuitos mediante el uso de un solo kit de evaluación.

# 1.2 Objetivos

El principal objetivo de este Proyecto de Fin de Carrera es el de realizar un estudio de forma experimental que permita definir cómo y en qué medida afectan las decisiones tomadas a la hora de diseñar un circuito digital al consumo final del mismo. Además, con el fin de extender la materia de estudio de este trabajo no sólo al diseño del circuito, sino también al ambiente que lo rodea, se estudiará cómo afecta un aumento de la temperatura del circuito al consumo del mismo.

Los hitos en los que puede dividirse este trabajo son:

- 1. Estudio del Estado del Arte referente a las diferentes técnicas de diseño de bajo consumo.

- 2. Elección de las herramientas de trabajo y aprendizaje de su correcta utilización.

- 3. Desarrollo de un *benchmark* de circuitos digitales que permita realizar numerosas mediciones y comparaciones entre las mismas.

- 4. Extracción y análisis de los resultados fruto del punto anterior.

- 5. Elaboración y presentación de conclusiones en base a dichos resultados.

# 1.3 Metodología

La metodología que se ha seguido a la hora de desarrollar este trabajo pasa por el cumplimiento de los hitos listados en el apartado previo, cada uno de los cuales han sido llevados a cabo siguiendo una metodología determinada que será detallada a continuación:

- 1. Estudio del Estado del Arte: el estudio del Estado del Arte se ha realizado a partir de una previa recopilación de diferentes libros y papers relacionados con la materia objeto de este proyecto, así como de diferentes hojas de datos y documentación sobre FPGAs y circuitos a un nivel más específico. Este punto busca no sólo presentar al lector la situación actual en lo referentes a circuitos de bajo consumo, sino también la adquisición de conocimientos relacionados con esta materia para poder así llevar a cabo el desarrollo de este trabajo.

- 2. *Elección de las herramientas de trabajo:* en primer lugar, se han identificado los objetivos que persigue este trabajo. Una vez hecho esto, se han barajado los diferentes medios de los que se disponían y seleccionado el kit de evaluación y la estufa de secado. Una vez hecho

esto y previamente al comienzo del desarrollo del proyecto, se ha dedicado un tiempo exclusivamente a realizar pruebas con el fin de familiarizarse con el material y aprender a usarlo correctamente para evitar así, por una parte, la posibilidad de causar daños en el material utilizado, y, por otra, la obtención de medidas erróneas que invaliden los resultados obtenidos a lo largo del desarrollo del proyecto.

- 3. **Desarrollo del benchmark:** antes de comenzar el desarrollo de la batería de circuitos utilizada para realizar las mediciones pertinentes, se ha realizado una planificación y un dimensionamiento de los diseños que serían objeto de prueba. Una vez hecho esto, se ha comenzado la implementación de los circuitos de prueba, agrupándolos siguiendo un criterio lógico. Además, ha resultado necesario diseñar una serie de circuitos auxiliares que permitieran el correcto funcionamiento de los circuitos objetos de estudio.

- 4. Extracción y análisis de resultados: la extracción de resultados se ha llevado a cabo manteniendo las condiciones externas al circuito lo más invariantes posible, de tal manera que las medidas extraídas de un mismo grupo de circuitos se ha realizado durante un período de tiempo lo más corto posible, para evitar que cambios de temperatura u otras magnitudes influyesen en los resultados extraídos. En cualquier caso, cualquier cambio detectable en alguna de estas magnitudes ha sido debidamente anotado. Los datos obtenidos se han agrupado y representado en gráficas y tablas de tal manera que puedan ser fácilmente interpretados a la hora de realizar un análisis de los mismos.

- 5. **Presentación de conclusiones:** una vez extraídos los datos fruto de la implementación y posterior medición de los diseños, se han presentado las conclusiones que se desprenden de ellos y las posibles líneas de trabajo futuro.

#### 1.4 Estructura

Este Proyecto de Fin de Carrera se divide en cinco capítulos:

- 1. *Introducción:* este capítulo presenta el trabajo realizado, exponiendo la motivación que impulsa el mismo, los objetivos que persigue, la metodología empleada y la estructura en la que se divide.

- 2. **Técnicas de Bajo Consumo para Diseño Digital:** en este capítulo se repasa el Estado del Arte en lo referente a Técnicas de Bajo Consumo para Diseño Digital, partiendo de una panorámica global y particularizando más a fondo conforme se ahonda en el mismo.

- 3. **Tecnología utilizada para el desarrollo del Proyecto:** este capítulo sirve para presentar y explicar las diferentes herramientas utilizadas durante el desarrollo del Proyecto, así como sus diversas especificaciones y funcionalidades.

- 4. **Presentación de resultados:** en este capítulo se presentan los resultados obtenidos de las mediciones realizadas en los circuitos que componen el *benchmark*, mediante tablas, gráficas, explicaciones breves y algunas comparativas.

- Desarrollo de conclusiones: finalmente, el propósito de este capítulo es presentar las conclusiones extraídas fruto del diseño de los circuitos y las subsecuentes mediciones realizadas en los mismos.

# 1.5 Siglas y acrónimos

• ALU: Arithmetic Logic Unit

- CLB: Configurable Logic Block

- **CMOS:** Complementary Metal-Oxide-Semiconductor

- CMT: Clock Management Tile

- CS: Chip Scale

- **CUT:** Circuit Under Test

- **DSP:** Digital Signal Processor

- **FPGA:** Field Programable Gate Array

- **FSM:** Finite-State Machine

- HDL: Hardware Description Language

- *IOB:* Input/Output Block

- **LFSR:** Linear Feedback Shift Register

- **LUT:** Look-Up Table

- **Pmod:** Peripheral Module

- **PSoC:** Programmable System-on-Chip

- **RTL:** Register-Transfer Level

- **SOI:** Silicon-On-Insulator

- VHDL: VHSIC Hardware Description Language

- VHSIC: Very High Speed Integrated Circuit

# Capítulo 2 – Técnicas de Bajo Consumo para Diseño Digital

En primer lugar, se procederá a realizar un repaso sucinto del Estado del Arte actual en lo referente a las diferentes técnicas de bajo consumo aplicadas a FPGAs, con el fin de conocer las circunstancias que rodean a la materia objeto de este proyecto y poder así encuadrarlo en su marco correspondiente.

## 2.1 Panorámica

Como ya se ha mencionado en el anterior capítulo, el objetivo último de este trabajo es el estudio del consumo de potencia en FPGAs y la definición de unas directrices de diseño que permitan minimizarlo. Con esta premisa en mente, se partirá de una visión general para posteriormente ir pormenorizando, presentando la materia a más bajo nivel y deteniéndose en los detalles.

Para poder modular una magnitud, independientemente de la dirección en la que se desee modificarla, resulta indispensable conocer su origen y su comportamiento. En definitiva, su naturaleza. Es por ello que en primer lugar de procederá a una presentación somera sobre las fuentes que originan el consumo de la potencia, cómo se comportan, cómo pueden modificarse en función de lo que busque el diseñador de circuitos y hasta qué punto puede esto hacerse.

# 2.2 Delimitación del espacio de trabajo

Para poder reducir el consumo de un circuito, se deben examinar los orígenes del mismo. Una vez hecho esto, se pueden establecer las restricciones que existen y determinar los límites dentro de los cuales se puede trabajar.

## 2.2.1 Fuentes de consumo<sup>1</sup>

En primer lugar y como parte central de esta sección, la ecuación que determina el consumo de un circuito de manera teórica e ideal es:

$$P = 0.5 C_L V_{dd}^2 E(sw) f_{clk}$$

<sup>2</sup>Ec. 1: Consumo de un circuito

Donde  $\mathcal{C}_L$  es la capacitancia física,  $V_{dd}$  es el voltaje de alimentación,  $\mathit{E(sw)}$  es el número de transiciones por segundo en la salida y  $f_{clk}$  es la frecuencia de funcionamiento del reloj del sistema.

<sup>&</sup>lt;sup>1</sup> Basado en "Sources of Power Dissipation", de Massoud Pedram en "Power Minimization in IC Design: Principles and Applications", January 1996

<sup>&</sup>lt;sup>2</sup> Massoud Pedram, "Power Minimization in IC Design: Principles and Applications", January 1996

La disipación de potencia en circuitos digitales CMOS procede principalmente de cuatro fuentes bien diferenciadas, que son:

- **Standby current (corriente en reposo):** es la corriente continua que ininterrumpidamente va desde VCC a GND, la que consume el circuito por el mero hecho de estar encendido, independientemente de las operaciones que esté ejecutando en un momento dado.

- Leakage current (corriente de fuga): se trata del flujo de corriente que se pierde de manera no intencionada en los condensadores que se hallan en un circuito debido a su naturaleza imperfecta.

- Capacitance current (corriente de capacitancia): procede del proceso de carga y descarga que tiene lugar en los condensadores que forman parte del circuito.

- Short-circuit current (corriente de cortocircuito): se produce en casos en los que se da una situación de baja resistencia, con el aumento de la misma, esta corriente se ve reducida progresivamente.

Considerando los puntos que originan el consumo en los circuitos electrónicos que van a analizarse a lo largo de este estudio, se puede proceder a establecer el espacio de trabajo en el que podrá llevarse a cabo.

Existen tres parámetros que delimitan significativamente la libertad dentro de la cual el diseñador de circuitos puede tomar decisiones:

- Voltaje

- Capacitancia física

- Actividad de datos dentro del circuito

La posibilidad de optimizar el consumo pasa forzosamente por reducir uno o más de los parámetros mencionados. A continuación se procederá a discutir qué caminos llevan a este objetivo y cómo estos parámetros interaccionan entre sí dificultando la tarea perseguida.

#### 2.2.2 Voltaje

El voltaje mantiene una estrecha relación con la potencia consumida por un circuito.

L potencia depende del cuadrado del voltaje, por lo que la reducción de este último se traducirá en una importante bajada del consumo. En otras palabras, el voltaje proporciona el camino más sencillo y efectivo hacia la optimización del consumo, una optimización que en este caso repercutirá en la totalidad del diseño.

Como contrapartida, el precio a pagar por esta reducción en el voltaje de entrada al circuito es una menor velocidad de operación por parte del mismo. Esta penalización crece considerablemente conforme el voltaje de alimentación se acerca al umbral del voltaje de funcionamiento de los transistores del circuito, lo cual limita significativamente su posible reducción. A la luz de este hecho, una disminución del voltaje de operación de estos transistores otorgará un mayor margen de reducción en el voltaje necesario la hora de alimentar el circuito.

El ajuste del voltaje de funcionamiento de los transistores debe ser determinado en función de la ganancia de corriente de las puertas CMOS en un régimen de bajo voltaje y el control de la *leakage*

current o corriente de fuga. Además, deben considerarse los márgenes de ruido permisibles para la aplicación concreta que se pretenda tratar.

## 2.2.3 Capacitancia

La minimización de las capacitancias de los elementos que conforman un circuito también permite reducir notablemente su consumo. Para poder modificar este parámetro, primero han de conocerse los diversos factores de los que depende el mismo.

En un caso ideal, la correlación entre el consumo del circuito y la capacitancia de sus elementos debe establecerse descendiendo hasta el más bajo nivel, las puertas individuales que componen el sistema. Sin embargo, estimar esta capacitancia individual de cada una de estas puertas es difícil e impreciso, pues requiere estimar las capacitancias de carga de estructuras que aún no han sido mapeadas y cuyo comportamiento dependerá de este subsecuente mapeo. Por esta razón, deberá realizarse una estimación a un nivel más global, considerando como elementos básicos los módulos operacionales del circuito, tales como operadores aritméticos, decodificadores o memorias. Esta estimación dependerá del número de entradas y salidas de cada elemento, de la complejidad del diseño y de la tecnología utilizada en la fabricación del mismo.

La interconexión de estos elementos complica aún más si cabe la tarea, dado que juega un papel determinante a la hora de establecer la capacitancia total resultante. Realizar una aproximación se antoja harto complicado cuando se carece de información precisa en lo que se refiere al rutado y mapeado. Esta falta de información detallada se puede suplir en caso de necesidad mediante el uso de una estimación probabilística.

A raíz de todo lo expuesto anteriormente, se puede establecer una correspondencia directa entre la capacitancia física y los siguientes puntos:

- Reducción de la lógica dentro del circuito

- Utilización de elementos de menor tamaño

- Disminución del número de cables

- Reducción de la longitud de los cables

Estas cuatro medidas contribuyen en diferente forma a la disminución de la capacitancia total del circuito. Las dos primeras permiten reducir la región activa del mismo, mientras que un cableado eficiente contribuirá a que la interconexión entre dispositivos no dispare la capacitancia.

De igual forma que en el caso expuesto anteriormente y referente al voltaje de operación, estas medidas suponen en muchos casos pagar un precio en forma de prestaciones, capacidad de operación o velocidad. Es por ello que será necesario encontrar una solución de compromiso entre los diferentes parámetros, estableciendo prioridades y determinando umbrales por debajo de los cuales no se esté dispuesto a llegar.

#### 2.2.4 Actividad de datos dentro del circuito

Cuantificar de manera precisa la actividad que se da durante un período de tiempo dentro de un circuito es una tarea compleja puesto que depende de un número de factores que no son fácilmente medibles o calculables. Dentro de este grupo de variables difíciles de caracterizar, se repasarán a continuación las más determinantes.

## 2.2.4.1 Patrón de la entrada de datos

Las transiciones en la salida de una puerta de un circuito no dependen únicamente de las transiciones ocurridas en las entradas, sino también de la lógica interna así como de las dependencias temporales y espaciales entre las propias entradas. En esta sección se analizará esta correlación entre entradas, más adelante se hará lo propio con la lógica mencionada. Por ejemplo, suponiendo una puerta OR con dos entradas independientes i y j, ambas con una probabilidad de ½ para 0 y 1 y una salida o. Para calcular la probabilidad de que se produzca una transición en la salida que implique consumo dinámico de potencia se considerará:

| Tabla de verdad de una puerta OR |   |   |  |  |  |

|----------------------------------|---|---|--|--|--|

| 1                                | J | 0 |  |  |  |

| 0                                | 0 | 0 |  |  |  |

| 0                                | 1 | 1 |  |  |  |

| 1                                | 0 | 1 |  |  |  |

| 1                                | 1 | 1 |  |  |  |

<sup>&</sup>lt;sup>3</sup> Tabla 1: Tabla de verdad OR

\_

| Tabla de posibles transiciones en una puerta OR |     |   |   |     |   |            |

|-------------------------------------------------|-----|---|---|-----|---|------------|

| i-1                                             | j-1 | 1 | j | o-1 | o | Transición |

| 0                                               | 0   | 0 | 0 | 0   | 0 | NO         |

| 0                                               | 0   | 0 | 1 | 0   | 1 | SÍ         |

| 0                                               | 0   | 1 | 0 | 0   | 1 | SÍ         |

| 0                                               | 0   | 1 | 1 | 0   | 1 | SÍ         |

| 0                                               | 1   | 0 | 0 | 1   | 0 | SÍ         |

| 0                                               | 1   | 0 | 1 | 1   | 1 | NO         |

| 0                                               | 1   | 1 | 0 | 1   | 1 | NO         |

| 0                                               | 1   | 1 | 1 | 1   | 1 | NO         |

| 1                                               | 0   | 0 | 0 | 1   | 0 | SÍ         |

| 1                                               | 0   | 0 | 1 | 1   | 1 | NO         |

| 1                                               | 0   | 1 | 0 | 1   | 1 | NO         |

| 1                                               | 0   | 1 | 1 | 1   | 1 | NO         |

| 1                                               | 1   | 0 | 0 | 1   | 0 | SÍ         |

| 1                                               | 1   | 0 | 1 | 1   | 1 | NO         |

| 1                                               | 1   | 1 | 0 | 1   | 1 | NO         |

| 1                                               | 1   | 1 | 1 | 1   | 1 | NO         |

<sup>4</sup>Tabla 2: Transiciones puerta OR

A la luz de lo analizado en estas tablas, puede establecerse que si consideramos los estados 0 y 1 como equiprobables en ambas entradas, todos los pasos de *o-1* a *o* lo serán también. Por lo tanto, para calcular la probabilidad de que se produzca una transición en la salida que implique consumo de potencia bastará con recurrir a la probabilidad clásica y establecer:

$$P(transición) = \frac{casos favorables (SÍ)}{casos totales (SÍ + NO)} = \frac{6}{16} = \frac{3}{8}$$

<sup>5</sup> Ec.2: Probabilidad de transición a la salida de un circuito

Por tanto, en el caso mencionado, después de realizar el análisis y los cálculos pertinentes, se llega a la conclusión de que la probabilidad de que se produzca una transición tras las llegada de dos nuevas entradas en un momento dado es de 3/8 o 0,375.

Para ilustrar el objetivo de este apartado, ahora se supondrá que las entradas i y j del circuito sólo pueden adoptar los valores ij=00 y ij=11, es decir, que ambas entradas compartirán siempre el mismo valor.

En este caso, la tabla de posibles transiciones se verá notablemente simplificada:

27

| Tabla de posibles transiciones en una puerta OR – Correlación espacial |     |   |   |     |   |            |

|------------------------------------------------------------------------|-----|---|---|-----|---|------------|

| i-1                                                                    | j-1 | i | j | o-1 | o | Transición |

| 0                                                                      | 0   | 0 | 0 | 0   | 0 | NO         |

| 0                                                                      | 0   | 1 | 1 | 0   | 1 | SÍ         |

| 1                                                                      | 1   | 0 | 0 | 1   | 0 | SÍ         |

| 1                                                                      | 1   | 1 | 1 | 1   | 1 | NO         |

<sup>6</sup>Tabla 3: Transiciones puerta OR

En este nuevo caso la posibilidad de obtener una transición se puede calcular nuevamente mediante el uso de la probabilidad clásica:

$$P(transición) = \frac{casos favorables (SÍ)}{casos totales (SÍ + NO)} = \frac{2}{4} = \frac{1}{2}$$

<sup>7</sup> Ec.3: Probabilidad de transición a la salida de un circuito

Mediante este sencillo cálculo se llega a la conclusión de que la probabilidad de obtener una transición en un cambio de las entradas puntual es en este caso diferente del anterior, resultado numéricamente 1/2 o 0,5.

Se contemplarán dos casos más con el fin de abundar en la dificultad que supone la estimación del consumo dinámico en lo relativo a la actividad de los datos dentro de un circuito cualquiera. En el siguiente de ellos, se considerará que forzosamente un 0 en la entrada *i* implicará un cambio a 1 en el siguiente ciclo mientras que un 1 en la entrada *j* vendrá siempre seguido de un 0. En este caso, la tabla de posibles valores y transiciones del circuito resultaría ser:

| Tabla de posibles transiciones en una puerta OR – Correlación temporal |     |   |   |     |   |            |

|------------------------------------------------------------------------|-----|---|---|-----|---|------------|

| i-1                                                                    | j-1 | i | j | o-1 | o | Transición |

| 0                                                                      | 0   | 1 | 0 | 0   | 1 | SÍ         |

| 0                                                                      | 0   | 1 | 1 | 0   | 1 | SÍ         |

| 0                                                                      | 1   | 1 | 0 | 1   | 1 | NO         |

| 1                                                                      | 0   | 0 | 0 | 1   | 0 | SÍ         |

| 1                                                                      | 0   | 0 | 1 | 1   | 1 | NO         |

| 1                                                                      | 0   | 1 | 0 | 1   | 1 | NO         |

| 1                                                                      | 0   | 1 | 1 | 1   | 1 | NO         |

| 1                                                                      | 1   | 0 | 0 | 1   | 0 | SÍ         |

| 1                                                                      | 1   | 1 | 0 | 1   | 1 | NO         |

<sup>&</sup>lt;sup>8</sup> Tabla 4: Transiciones puerta OR

28

En este caso, y análogamente a los anteriores, la probabilidad de obtener una transición 0-1 o 1-0 en la salida del circuito, vendrá dada por:

$$P(transición) = \frac{casos favorables (SÍ)}{casos totales (SÍ + NO)} = \frac{4}{9}$$

<sup>9</sup>Ec.4: Probabilidad de transición a la salida de un circuito

Como cabía esperar, nuevamente se obtiene un resultado que difiere de los dos calculados en apartados previos, en este caso 4/9 o 0,44.

Para finalizar, se establecerá un último caso de dependencia entre datos subsecuentes a la entrada del circuito y una vez hecho esto, se examinarán los diferentes tipos de correlaciones.

En este último caso, se supondrá la entrada *i* del circuito sólo cambiará en los casos en los que la entrada *j* cambie, mientras que en el resto permanecerá invariable. Esta dependencia entre entradas ocurrirá en ambas direcciones, implicando esto que *j* sólo modificará su valor cuando lo haga *i*. En otras palabras, los cambios en las entradas siempre se producirán de manera simultánea.

A continuación se detallan las posibles entradas, salidas y la comprobación de si se produce o no transición, en una tabla análoga a las mostradas en los casos previos:

| Tabla de posibles transiciones en una puerta OR – Correlación espacio-temporal |   |     |   |     |   |            |

|--------------------------------------------------------------------------------|---|-----|---|-----|---|------------|

| i-1                                                                            | 1 | j-1 | j | o-1 | o | Transición |

| 0                                                                              | 0 | 0   | 0 | 0   | 0 | NO         |

| 0                                                                              | 0 | 1   | 1 | 0   | 1 | SÍ         |

| 0                                                                              | 1 | 0   | 1 | 1   | 1 | NO         |

| 0                                                                              | 1 | 1   | 0 | 1   | 1 | NO         |

| 1                                                                              | 0 | 0   | 1 | 1   | 1 | NO         |

| 1                                                                              | 0 | 1   | 0 | 1   | 1 | NO         |

| 1                                                                              | 1 | 0   | 0 | 1   | 0 | SÍ         |

| 1                                                                              | 1 | 1   | 1 | 1   | 1 | NO         |

<sup>10</sup>Tabla 5: Transiciones puerta OR

En este caso, la probabilidad de que se produzca una transición que implique consumo de potencia en un cambio de entradas concreto vendrá dada por:

$$P(transición) = \frac{casos favorables (SÍ)}{casos totales (SÍ + NO)} = \frac{2}{8} = \frac{1}{4}$$

<sup>11</sup>Ec.5: Probabilidad de transición a la salida de un circuito

La probabilidad en este caso valdrá 1/4 o 0,25, nuevamente un valor que difiere de todos los calculados para los casos previos.

Para un mismo tipo de puerta, OR en este caso, se han mostrado 4 patrones diferentes de entrada, ofreciendo cada uno de ellos una probabilidad diferente de producir una transición en su salida en un momento dado. Los casos no han sido elegidos al azar, sino pretendiendo ilustrar en cada uno de ellos una clase diferente de correlación entre datos de entrada subsecuentes:

- Primer caso entradas sin correlación: entradas sin ningún tipo de dependencia entre ellas.

- Segundo caso entradas con correlación espacial: entradas que guardan una dependencia espacial entre ellas, el valor de la entrada i determina el valor de la entrada j en el ciclo de operación presente y viceversa.

- Tercer caso entradas con correlación temporal: entradas que guardan una dependencia temporal entre ellas, sus valores presentes condicionarán en ciertos casos sus valores futuros. El valor de la entrada i determina que ocurra o no una transición en esa misma entrada en un ciclo de operación futuro. Este comportamiento es análogo en el caso de la entrada j.

- Cuarto caso entradas con correlación espaciotemporal: entradas que guardan una dependencia espaciotemporal entre ellas, sus transiciones implicarán otras transiciones en el mismo ciclo de operación en el que se producen. Una transición en la entrada *i* implicará una transición en la entrada *j* y viceversa, es decir, ambas transiciones ocurrirán simultáneamente o no ocurrirán.

Los diversos casos de correlación entre diferentes entradas, presentados para un circuito tan simple como puede ser una puerta lógica OR, ilustran de manera clara lo que se pretende, la fuerte dependencia entre el patrón que rige las entradas de un circuito y el consumo dinámico del mismo. Tras esta relación subyace un problema de importancia mayúscula; resulta complejo a efectos prácticos estimar la potencia consumida tomando como base un análisis exhaustivo de la simulación del circuito.

Es por ello que existen técnicas que, basándose en un modelo probabilístico, describen el conjunto de posibles valores lógicos en las entradas de un circuito y desarrollan mecanismos de cálculo que permiten calcular las probabilidades para las puertas internas del mismo.

Otra alternativa factible a la simulación exhaustiva que ya se ha descartado es la del muestreo estadístico. Esta técnica, habiendo definido mediante un buen criterio los límites del mismo en función de los márgenes de error deseados, ofrece también resultados con un nivel de confianza aceptable.

#### 2.2.4.2 Modelo de retardo

A la hora de realizar una estimación del consumo de un circuito es de vital importancia considerar qué y cuántas transiciones se producen en su interior. Para ello, han de tenerse en cuenta todas ellas, independientemente de su naturaleza, y pueden ser:

- Transiciones de carácter computacional: estas transiciones son completamente necesarias

para que un circuito funcione correctamente, se producen como resultado de la actividad

funcional del circuito en sí mismo.

- Transiciones de carácter espurio: estas transiciones no son ni necesarias ni deseadas en el funcionamiento de un circuito. Sin embargo, ocurren inevitablemente por estar tratando un modelo de estudio real, no ideal, y han de ser consideradas ya que en determinados circuitos pueden suponer una parte importante de la actividad total del mismo. Son también conocidas como glitches.

Todas estas transiciones se ven afectadas de forma inevitable por retardos de procesamiento y propagación a lo largo de todo el circuito. Estos retardos se analizarán en base a un modelo. El modelo de retardo tenido en cuenta a la hora de estimar el consumo ocasionado por un circuito específico determinará en buena parte el resultado de esta estimación. Las posibles opciones a la hora de incorporar estas consideraciones al consumo de potencia son:

- *Modelo ideal:* en esta aproximación se considerará que todos los cambios en los componentes del circuito se propagan entre las diferentes puertas de manera instantánea.

- Modelo real: este modelo considera la existencia de retardos a la hora de producirse la

propagación de datos dentro del circuito. Asigna a cada puerta del circuito un retardo finito

y tiene en cuenta los posibles glitches que puedan aparecer durante su funcionamiento.

Este modelo tiene unos requerimientos computacionales más elevados, pero como

contrapartida ofrece unos resultados muchos más próximos a la realidad.

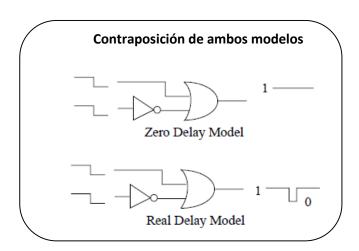

<sup>12</sup>Fig.1: Contraposición modelo real-ideal

El cálculo de la actividad espuria previamente mencionada presenta, en términos generales, una dificultad elevada y requiere de una caracterización cuidadosa tanto a nivel lógico como a nivel de circuitería de las puertas utilizadas en el diseño, así como un conocimiento profundo de la estructura del circuito en sí mismo. Los principales problemas se presentan a la hora de determinar

\_

<sup>&</sup>lt;sup>12</sup> Massoud Pedram, "Power Minimization in IC Design: Principles and Applications", January 1996

cuándo y en qué sección o secciones del circuito se producen los comportamientos indeseados y en qué forma y hasta qué punto avanzará esta irregularidad hasta ser suprimida.

La mayor problemática la entraña precisamente este segundo punto. Reproducir esta propagación usando un modelo de retardo real supone un proceso analógico costoso y que requiere de una gran precisión a la hora de hacer el análisis del circuito.

En redes de circuitos reales, las perturbaciones estadísticas de los parámetros de un circuito en particular puede modificar el retardo de propagación y, de esta forma, implicar cambios en el número de transiciones que se producirán debido a la posible aparición y desaparición de actividad espuria.

## 2.2.4.3 Funciones lógicas

La frecuencia y la cantidad total de las transiciones a la salida de una puerta lógica están estrechamente relacionadas con la función booleana de la puerta en sí misma. Esta dependencia se debe, como resulta obvio, a que es la función lógica de la puerta la que determina cual es la probabilidad de obtener una salida u otra. De esta forma, al influir de manera determinante sobre la salida que se obtendrá en cada caso, influye de igual manera en la transición entre salidas subsecuentes, y por tanto, en la posibilidad de que exista o no transición entre dichas salidas, lo cual en última instancia determinará si hay o no un aumento en el consumo del circuito.

Para ilustrar la importancia de este punto, se supondrá que se tienen dos señales que no guardan ninguna relación entre sí y que además pueden adoptar los valores 0 y 1 en un momento determinado con la misma probabilidad. En este escenario, se considerarán las puertas AND y XOR.

| Tabla de verdad de una puerta AND |   |   |  |  |  |

|-----------------------------------|---|---|--|--|--|

| i                                 | j | 0 |  |  |  |

| 0                                 | 0 | 0 |  |  |  |

| 0                                 | 1 | 0 |  |  |  |

| 1                                 | 0 | 0 |  |  |  |

| 1                                 | 1 | 1 |  |  |  |

13 Tabla 6: Tabla de verdad AND

| Tabla de verdad de una puerta XOR |   |   |  |  |  |

|-----------------------------------|---|---|--|--|--|

| i                                 | j | 0 |  |  |  |

| 0                                 | 0 | 0 |  |  |  |

| 0                                 | 1 | 1 |  |  |  |

| 1                                 | 0 | 1 |  |  |  |

| 1                                 | 1 | 0 |  |  |  |

<sup>14</sup> Tabla 7: Tabla de verdad XOR

Dadas las tablas de verdad de ambas puertas lógicas, AND y XOR, se puede comprobar que, efectivamente, las probabilidades de obtener una u otra salida en cada una de ellas considerando patrones de entrada completamente aleatorios y equiprobables son diferentes.

$$P(0/AND) = \frac{casos\ favorables\ (0)}{casos\ totales\ (0+1)} = \frac{3}{4}$$

$$P(1/AND) = \frac{casos\ favorables\ (1)}{casos\ totales\ (0+1)} = \frac{1}{4}$$

$$P(0/XOR) = \frac{casos\ favorables\ (0)}{casos\ totales\ (0+1)} = \frac{2}{4} = \frac{1}{2}$$

$$P(1/XOR) = \frac{casos\ favorables\ (1)}{casos\ totales\ (0+1)} = \frac{2}{4} = \frac{1}{2}$$

<sup>15</sup> Ec.6: Probabilidad de transición a la salida de un circuito

Esta diferencia de probabilidades implica también diferencias la salida.

| Tabla de posibles transiciones en una puerta AND |     |   |   |     |   |            |

|--------------------------------------------------|-----|---|---|-----|---|------------|

| i-1                                              | j-1 | i | j | o-1 | О | Transición |

| 0                                                | 0   | 0 | 0 | 0   | 0 | NO         |

| 0                                                | 0   | 0 | 1 | 0   | 0 | NO         |

| 0                                                | 0   | 1 | 0 | 0   | 0 | NO         |

| 0                                                | 0   | 1 | 1 | 0   | 1 | SÍ         |

| 0                                                | 1   | 0 | 0 | 0   | 0 | NO         |

| 0                                                | 1   | 0 | 1 | 0   | 0 | NO         |

| 0                                                | 1   | 1 | 0 | 0   | 0 | NO         |

| 0                                                | 1   | 1 | 1 | 0   | 1 | SÍ         |

| 1                                                | 0   | 0 | 0 | 0   | 0 | NO         |

| 1                                                | 0   | 0 | 1 | 0   | 0 | NO         |

| 1                                                | 0   | 1 | 0 | 0   | 0 | NO         |

| 1                                                | 0   | 1 | 1 | 0   | 1 | SÍ         |

| 1                                                | 1   | 0 | 0 | 1   | 0 | SÍ         |

| 1                                                | 1   | 0 | 1 | 1   | 0 | SÍ         |

| 1                                                | 1   | 1 | 0 | 1   | 0 | SÍ         |

| 1                                                | 1   | 1 | 1 | 1   | 1 | NO         |

<sup>&</sup>lt;sup>16</sup> Tabla 8: Transiciones puerta AND

33

La probabilidad de obtener una transición entre dos datos consecutivos a la salida de una puerta AND en un momento determinado vendrá dada por:

$$P(transición) = \frac{casos favorables (SÍ)}{casos totales (SÍ + NO)} = \frac{6}{16} = \frac{3}{8}$$

<sup>17</sup>Ec.7: Probabilidad de transición a la salida de un circuito

A continuación se presentará el caso análogo, utilizando en este caso una puerta XOR para ilustrar la discrepancia existente entre diferentes circuitos la hora de considerar la frecuencia de transiciones en la salida.

| Tabla de posibles transiciones en una puerta XOR |     |   |   |     |   |            |

|--------------------------------------------------|-----|---|---|-----|---|------------|

| i-1                                              | j-1 | i | j | o-1 | o | Transición |

| 0                                                | 0   | 0 | 0 | 0   | 0 | NO         |

| 0                                                | 0   | 0 | 1 | 0   | 1 | SÍ         |

| 0                                                | 0   | 1 | 0 | 0   | 1 | SÍ         |

| 0                                                | 0   | 1 | 1 | 0   | 0 | NO         |

| 0                                                | 1   | 0 | 0 | 1   | 0 | SÍ         |

| 0                                                | 1   | 0 | 1 | 1   | 1 | NO         |

| 0                                                | 1   | 1 | 0 | 1   | 1 | NO         |

| 0                                                | 1   | 1 | 1 | 1   | 0 | SÍ         |

| 1                                                | 0   | 0 | 0 | 1   | 0 | SÍ         |

| 1                                                | 0   | 0 | 1 | 1   | 1 | NO         |

| 1                                                | 0   | 1 | 0 | 1   | 1 | NO         |

| 1                                                | 0   | 1 | 1 | 1   | 0 | SÍ         |

| 1                                                | 1   | 0 | 0 | 0   | 0 | NO         |

| 1                                                | 1   | 0 | 1 | 0   | 1 | SÍ         |

| 1                                                | 1   | 1 | 0 | 0   | 1 | SÍ         |

| 1                                                | 1   | 1 | 1 | 0   | 0 | NO         |

<sup>&</sup>lt;sup>18</sup> Tabla 9: Transiciones puerta XOR

En el caso de la puerta XOR, la probabilidad de obtener de obtener una transición entre dos salidas consecutivas para un momento dado vendrá dada por:

$$P(transición) = \frac{casos favorables (SÍ)}{casos totales (SÍ + NO)} = \frac{8}{16} = \frac{1}{2}$$

<sup>19</sup>Ec.8: Probabilidad de transición a la salida de un circuito

A la luz de los resultados extraídos para cada caso y por comparación entre ambos, queda patente la fuerte dependencia que existe entre el tipo de puerta tratado y la frecuencia de las transiciones que se darán en su salida. Desde este punto se puede inferir que esta correlación mostrada para el caso de una sola puerta tendrá aún mayores implicaciones para el caso de un circuito complejo con un número de puertas mayor.

Se ha considerado únicamente el caso de puertas de dos entradas con el fin de no abundar demasiado en una sola idea, pero lo mostrado en este apartado se hace extensible a un posible caso en el que las puertas posean K salidas, siendo K un número entero positivo mayor que 2. En el caso de la puerta XOR, por ejemplo, la probabilidad de transición se mantendrá en 1/2 independientemente del número de entradas considerado. En el caso de la puerta AND, sin embargo, un aumento hasta K entradas implicará que la probabilidad de obtener un 1 a la salida será de  $1/2^K$ , lo cual implica que únicamente existirá transición a la salida con probabilidad  $1/2^{K-1}$ . La diferencia entre los resultados obtenidos en uno y otro caso se vuelve aún mayor.

#### 2.2.4.4 Lógica estática vs. lógica dinámica

La actividad en circuitos CMOS es también función del estilo lógico utilizado para implementar el propio circuito. Un buen ejemplo de esto se obtiene al considerar la contraposición entre lógica dinámica y lógica estática.

La actividad en un circuito dinámico es siempre más alta que en la implementación estática del mismo circuito, en buena parte debido a que todos los nodos están precargados con algún valor antes de que aparezca una nueva entrada. Este valor precargado será 1 para los transistores tipo N en el caso dinámico y 0 para los transistores tipo P también en el caso dinámico. Esto, en efecto, aumenta el número de transiciones y dispara el consumo del circuito.

Por otra parte, cabe destacar que en el caso estático la capacitancia física tiende a adoptar valores más pequeños en circuitos estáticos, si bien es cierto que los circuitos dinámicos están libres de *glitches*. Por último, cabe destacar que los segundos consumen mucha potencia adicional debido al reloj.

Habiendo puesto de relieve las características de uno y otro modelo, puede establecerse que la elección de uno u otro no resulta algo sencillo, no existe un umbral que permita discriminarlos. Debe examinarse cada caso particular de manera minuciosa, sopesar pros y contras y tomar una decisión después de estudiarlos cuidadosamente.

#### 2.2.4.5 Estructura del circuito

Otra de las grandes dificultades la hora de estimar la cantidad y frecuencia de las transiciones de un circuito reside en su propia estructura. El problema del *fanout*, que se da en el caso en el que un número de entradas mayor que uno convergen en un mismo *n*odo dentro del circuito, conlleva complicaciones notables en el cálculo que es objeto de estudio.

Suponiendo el ejemplo de un circuito compuesto únicamente de puertas simples y no presente ningún nodo que reciba más de una entrada, la actividad del mismo puede ser calculada de manera sensiblemente más sencilla que en el caso contrario. Un circuito en el que exista una fuerte presencia de *fanout* se complicará enormemente este cálculo o estimación. Esto ocurrirá debido a

que las señales internas se vuelven fuertemente correlacionadas entre sí y la consideración de estas correlaciones no puede llevarse a cabo sin una gran carga computacional o uso masivo de memoria.

En estos casos, se suele proceder o bien ignorando esta correlación a la hora de realizar los cálculos o bien realizando una aproximación que ofrecerá resultados más precisos conforme se destinen más recursos a ella.

#### 2.3 Técnicas de estimación de consumo en circuitos

Hasta este momento se han recogido los diferentes parámetros que han de ser considerados a la hora de buscar la reducción del consumo en circuitos digitales. Para lograr este objetivo, resulta de vital importancia contar con una técnica depurada y fiable que permita realizar medidas de confianza, para poder así establecer qué técnicas e iniciativas nos consumen más y cuáles consumen menos. Resulta evidente que si no se dispone de herramientas de medición precisas, resultará imposible determinar qué técnicas de diseño ofrecerán mejores resultados. A continuación se realiza un repaso sucinto de las técnicas de estimación de consumo más utilizadas.

#### 2.3.1 Técnicas de simulación<sup>20</sup>

Este planteamiento se nutre de las simulaciones directas y las técnicas de muestreo que se detallarán más adelante. La principal ventaja que ofrecen es la preexistencia de simuladores que pueden ser utilizados y que pueden tomar en consideración los puntos mencionados anteriormente, tales como el *fanout* o los retardos de propagación. Existen diferentes planteamientos al respecto.

#### 2.3.1.1 Simulación directa

La simulación directa consiste en recrear el circuito con una entrada representativa de vectores de entrada. Existen modelos y dispositivos que ofrecen usabilidad, capacidad de adaptarse a múltiples diseños, la posibilidad de trabajar con un reloj multifase o de fase única, *buffers* triestado y otras capacidades.

Como contrapartida, este planteamiento adolece de un gran consumo tanto de memoria como de tiempo, limitaciones que lo hacen inadecuado para diseños de grandes dimensiones. Otra desventaja reside en la dificultad de generar un vector de estímulos compacto que permita calcular con precisión la actividad que ocurre en los diferentes nodos del circuito. Este vector es dependiente de la aplicación objeto de estudio y del entorno del sistema.

# 2.3.1.2 Simulación jerarquizada

La idea detrás de este método consiste en realizar una simulación basada en varios simuladores de diferente jerarquía. De esta forma se pretende alcanzar una relación entre precisión y eficiencia razonable. Un ejemplo de este planteamiento sería el de una simulación que compute la información de la actividad dentro del circuito y otra que se encargue de caracterizar los parámetros relativos al consumo del mismo.

$<sup>^{20}</sup>$  Basado en "Simulative Techniques", de Massoud Pedram en "Power Minimization in IC Design: Principles and Applications", January 1996

#### 2.3.1.3 Muestreo estadístico

En este caso se trata de realizar una estimación estadística que permita seleccionar los vectores de entrada más representativos de tal manera que la consecuente simulación arroje resultados consistentes.

El método de Montecarlo funciona razonablemente bien en esta situación. Este planteamiento consiste en aplicar patrones de entrada generados de forma aleatoria y monitorizar la potencia disipada para un número fijo de ciclos de reloj. Cada medida obtenida se considera una muestra de potencia disipada y todas ellas constituyen una variable aleatoria. Por el Teorema Central del Límite, conforme el número de ciclos de reloj considerados aumenta, la densidad del muestreo tiende a formar una curva gaussiana. A efectos prácticos, un tamaño muestral de entre 30 y 50 unidades cumple con este hecho para la mayoría de circuitos combinacionales. Para un control mayor de los diferentes parámetros implicados y la obtención de un error máximo en la estimación, puede hacerse uso de la siguiente fórmula:

$$N = \left(\frac{Z_{\alpha/2} \, \sigma}{E}\right)^2$$

<sup>21</sup>Ec.9: Número de muestras requerido para la estimación del consumo

Donde E es el error máximo deseado, 1- $\alpha$  el intervalo de confianza,  $\sigma$  la desviación típica de la muestra, N el número de muestras requerido y  $Z_{\alpha/2}$  es el punto definido de tal manera que el área hacia su derecha debajo de la curva gaussiana sea igual a  $\alpha/2$ . De esta manera, se fija el mínimo número de muestras necesario para un error máximo fijado. Igualando o superando este número, se puede esperar obtener los resultados deseados con el nivel de confianza previamente fijado.

El método de Montecarlo ofrece resultados razonablemente precisos para situaciones en las que los límites del error no se alejen demasiado de la media o bien el nivel de confianza requerido sea bajo. Nótese, sin embargo, que esta aproximación puede converger prematuramente a una potencia estimada lejos de la real si la densidad de la muestra no presenta una distribución gaussiana, lo cual ocurrirá si el número de ciclos de reloj es demasiado pequeño. Además, este planteamiento no considera la correlación espacial en las entradas del circuito.

#### 2.3.2 Técnicas alternativas a la simulación<sup>22</sup>

Este planteamiento está basado en modelos estocásticos, teóricos o basados en diferentes librerías. Se pueden considerar diferentes niveles a la hora de realizar el análisis y la posterior estimación.

#### 2.3.2.1 Estimación a nivel de comportamiento del circuito

Para unidades funcionales simples, tales como sumadores, multiplicadores y registros, así como para memorias, las estimaciones de consumo pueden obtenerse directamente de la librería de

<sup>&</sup>lt;sup>21</sup> Héctor Quintero y Guillermo Bianchi, "Técnicas de Muestreo", April 2012

<sup>&</sup>lt;sup>22</sup> Basado en "Non-Simulative Approaches", de Massoud Pedram en "Power Minimization in IC Design: Principles and Applications", January 1996

diseño donde se encuentran. En ella, las diversas unidades han sido diseñadas considerando un ruido blanco pseudoaleatorio, así como una capacitancia predefinida.

De esta manera, el modelo de consumo de un elemento puede ser parametrizado en términos de la anchura de su entrada. Por ejemplo, el consumo de una unidad aritmética como puede ser un sumador guarda una relación de dependencia directa y lineal con respecto a su número de entradas. En el caso del multiplicador, esta relación pasa a ser cuadrática.

Las distintas librerías contienen, así, descripciones detalladas de cada módulo, así como de sus diferentes parámetros, el área que ocupan, sus retardos y su potencia disipada de manera interna. Para poder llegar a este punto y estimar el consumo de las diferentes unidades, se procede a considerar ellos elementos a nivel lógico. Una vez hecho esto, se generan largas cadenas de entrada con patrones de entrada aleatorios y se calcula el consumo medio para cada patrón. En el caso de unidades con diferentes funciones, como bien pudiera ser una *ALU*, se estudia cada uno de sus comportamientos por separado. Los modelos generados son almacenados para cada módulo en la librería y deben presentar la posibilidad de ser en cierto modo condicionados o modulados, es decir, depender en cierto grado de las entradas que le son asignadas.

### 2.3.2.2 Estimación a nivel lógico

#### 2.3.2.2.1 Estimación para el modelo ideal

La mayor parte de la potencia disipada en circuitos procede de la carga y la descarga de la carga capacitiva de los mismos. Para estimar el consumo han de calcularse los diversos factores que afectan a la cantidad de transiciones en los nodos internos del circuito. Los métodos que permiten llevar esto a cabo pasan por la estimación de la probabilidad de que el valor de la señal en el nodo en un momento dado sea 1. Bajo la asunción de que los valores para la entrada de cada circuito son temporalmente independientes, puede establecerse lo siguiente:

$$E_n(sw) = 2 \operatorname{prob}(n) (1 - \operatorname{prob}(n)).$$

<sup>23</sup>Ec.10: Factor de actividad dentro de un circuito

Donde  $E_n(sw)$  es el factor de actividad dentro del circuito, una medida de la frecuencia de las transiciones que se producen, y prob(n), la probabilidad de que el nodo tenga valor 1 en un momento dado.

Una vez hecho esto, se asocian nombres a los nodos del circuito, se calculan las expresiones de cada uno de estos nodos, y a partir de estas se establece una expresión global para cada línea del circuito. Aunque el algoritmo en sí mismo resulta simple y general, la complejidad de este método en cuanto a tiempo empleado en el mismo aumenta significativamente con el tamaño del circuito.

#### 2.3.2.2.2 Estimación para el modelo real

La estimación presentada en el apartado anterior no considera las transiciones de carácter espurio o *glitches*, así como otros comportamientos indeseados dentro del circuito. A continuación se

<sup>&</sup>lt;sup>23</sup> Massoud Pedram, "Power Minimization in IC Design: Principles and Applications", January 1996

mostrarán las técnicas que permiten realizar una estimación considerando todos estos puntos que se alejan del modelo ideal.

En el caso anterior, se hablaba de la probabilidad de encontrar un 1 o un 0 en un nodo concreto del circuito estudiado para un momento dado. A partir de ese punto, obteniendo expresiones algebraicas sencillas y agrupándolas como una expresión más compleja, se obtenía una estimación razonablemente precisa de la actividad dada dentro del circuito.

En el caso actual, se sustituirá esa idea de probabilidad de encontrar un valor booleano, por la idea de una probabilidad que modele una forma de onda.

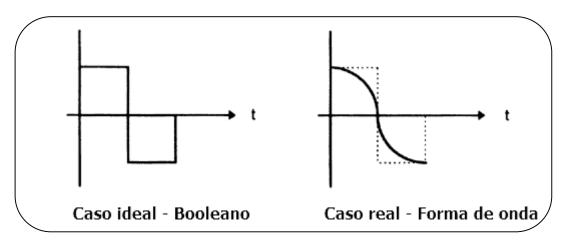

<sup>24</sup>Fig.2: Contraposición booleano-forma de onda

El concepto de probabilidad de la forma de onda, análogamente a la definición de la propia probabilidad en sí misma, es una secuencia de transiciones continuas o eventos en el tiempo desde un instante inicial t=0 hasta t=  $\infty$  para la cual cada evento es anotado con su probabilidad de ocurrencia correspondiente. De esta manera, resulta ser una representación compacta de todas las posibles formas de onda que pueden darse en ese nodo. Dada esta función, estimar la actividad en ese nodo considerando *glitches* y otros comportamientos no deseados será posible dada la siguiente expresión, análoga a la del apartado anterior: