# Universidad Autónoma de Madrid

ESCUELA POLITÉCNICA SUPERIOR

Proyecto fin de carrera

# CONTROL DIGITAL DE CONVERTIDOR CONMUTADO MEDIANTE FPGA MIXTA ANALÓGICA/DIGITAL

Ingeniería de Telecomunicación

Patricia Cuesta Marcos Julio 2015

# CONTROL DIGITAL DE CONVERTIDOR CONMUTADO MEDIANTE FPGA MIXTA ANALÓGICA/DIGITAL

AUTOR: Patricia Cuesta Marcos TUTOR: Ángel de Castro Martín

Human Computer Technology Laboratory (HCTLab) Escuela Politécnica Superior Universidad Autónoma de Madrid Julio 2015

# Resumen

## Resumen

El presente proyecto tiene como objetivo la regulación de la tensión de salida de un convertidor Boost Elevador mediante controles en lazo cerrado.

La regulación se llevará a cabo mediante la placa de desarrollo "Actel Fusion Kit" de Microsemi. Destacar que la FPGA incluida en la placa de desarrollo utilizada, además de contar con un bloque digital, cuenta con un bloque analógico a través del cual será posible llevar a cabo las conversiones analógica a digital.

En primer lugar, se llevará a cabo la regulación mediante un control por medio de un único lazo de tensión y por último, se llevará a cabo la regulación por medio de un control de doble lazo. Este control utilizará un lazo rápido de corriente y un lazo lento de tensión.

# Abstract

This project aims to regulate the output voltage of a Boost converter by different closed loop controls.

The regulation will take place with the development board provided in Microsemi's "Actel Fusion Kit". The FPGA included in the development board incorperates an analog block in addition to the digital one. This analog block will be reponsible of carring out the analog-to-digital conversions.

First of all, a single voltage loop will be implemented. Secondly, a double loop control will be implemented to control the output voltage of the Boost Converter. The double control loop consists of a fast current loop and a slow voltage loop interaction.

# Agradecimientos

Agradecer en primer lugar a mi tutor Ángel la labor de dirección y supervisión realizada, sin la cual este proyecto no hubiera sido posible. También agradecer al HCTLab haberme acogido.

A todos esos amigos con los que he compartido el tiempo a lo largo de estos años.

A mis compañeros de trabajo, por dejarme escapar cuando lo he necesitado.

A mi familia, por su apoyo incondicional, y en especial a Miguel, por toda su paciencia.

A Paco, por permanecer a mi lado durante todos estos años, tanto en los buenos, como en los malos momentos.

A mis padres, Marcelino y Mercedes, que sin ellos nada de esto hubiera sido posible.

Y en último lugar, pero no menos importante, a mi hermano, Alberto, a quien dedico este proyecto porque ¿Qué haría yo sin el?.

Muchas gracias a todos.

# Índice general

| Αţ | grade | ecimiei | 1tos                                               | V  |

|----|-------|---------|----------------------------------------------------|----|

| Ín | dice  | de figu | ıras                                               | X  |

| 1. | Intr  | oducci  | ión y Estado del Arte                              | 1  |

|    | 1.1.  | Antec   | edentes Históricos                                 | 1  |

|    | 1.2.  | Estado  | o del Arte                                         | 3  |

|    |       | 1.2.1.  | Fuentes de alimentación                            | 3  |

|    |       | 1.2.2.  | Sistemas de Control                                | 5  |

|    |       | 1.2.3.  | Factor de Potencia                                 | 10 |

|    | 1.3.  | Objeti  | vos del proyecto                                   | 14 |

| 2. | Tec   | nología | a utilizada                                        | 17 |

|    | 2.1.  | "Fusio" | n Starter Kit"                                     | 17 |

|    |       | 2.1.1.  | Bloque Digital                                     | 19 |

|    |       | 2.1.2.  | Bloque Analógico de la FPGA AFS600                 | 19 |

|    | 2.2.  | Herra   | nientas Software Utilizadas                        | 23 |

|    |       | 2.2.1.  | Matlab                                             | 24 |

|    |       | 2.2.2.  | ModelSim                                           | 25 |

|    |       | 2.2.3.  | Libero IDE                                         | 25 |

| 3. | Con   | vertid  | or Boost Elevador                                  | 31 |

|    | 3.1.  | Conve   | rtidor Boost Elevador                              | 31 |

|    |       | 3.1.1.  | MCC - Modo de Conducción Continuo                  | 32 |

|    |       | 3.1.2.  | MCD - Modo de Conducción Discontinua               | 34 |

|    | 3.2.  | Boost   | Utilizado                                          | 36 |

| 4. | Est   | rategia | de control                                         | 39 |

|    | 4.1.  | Contro  | oladores Digitales                                 | 39 |

|    |       | 4.1.1.  | Fundamentos Matemáticos de los Sistemas de Control | 41 |

|    |       | 4 1 0   | Cittana da Cantal da Tara Canada                   | 40 |

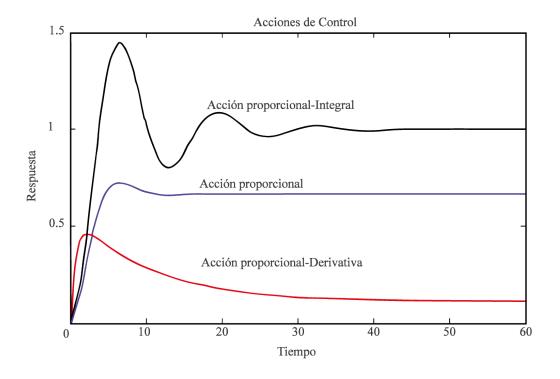

|                  |        | 4.1.3.  | Acciones de Control                          |   |  |   |   | 43         |

|------------------|--------|---------|----------------------------------------------|---|--|---|---|------------|

|                  |        | 4.1.4.  | Estructuras de Control                       |   |  |   |   | 45         |

|                  | 4.2.   | Diseño  | del Lazo de Tensión                          |   |  |   |   | 49         |

|                  |        | 4.2.1.  | Diseño del Controlador                       |   |  |   |   | 51         |

|                  | 4.3.   | Diseño  | del Doble Lazo                               |   |  |   |   | 52         |

|                  |        | 4.3.1.  | Diseño de Controladores                      |   |  |   |   | 54         |

|                  | 4.4.   | Implen  | nentación de los Lazos                       |   |  |   |   | 57         |

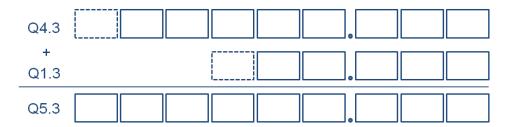

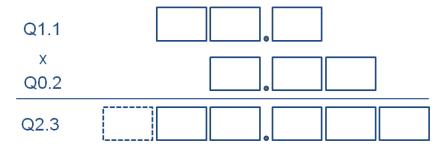

|                  |        | 4.4.1.  | Formato QX.Y                                 |   |  | • |   | 58         |

|                  |        | 4.4.2.  | Implementación de Funciones de Transferencia |   |  |   |   | 59         |

| 5.               | Sim    | ulacion | es                                           |   |  |   |   | 61         |

|                  | 5.1.   | Modelo  | os VHDL                                      |   |  |   |   | 61         |

|                  | 5.2.   | Contro  | ladores                                      |   |  |   |   | 63         |

|                  |        | 5.2.1.  | Control de Lazo de Tensión                   |   |  |   |   | 63         |

|                  |        | 5.2.2.  | Control de Doble Lazo                        | • |  |   |   | 65         |

| 6.               | Pru    | ebas E  | xperimentales                                |   |  |   |   | 69         |

|                  | 6.1.   | Resulta | ados Experimentales                          |   |  | • |   | 69         |

|                  |        | 6.1.1.  | Control de Lazo de Tensión                   |   |  |   |   | 70         |

|                  |        | 6.1.2.  | Control de Doble Lazo                        |   |  |   |   | 76         |

|                  |        | 6.1.3.  | Resultados en Lazo Cerrado                   | į |  |   |   | 77         |

| 7.               | Con    | clusior | ies y Trabajo Futuro                         |   |  |   |   | <b>7</b> 9 |

|                  | 7.1.   | Conclu  | siones                                       |   |  |   |   | 79         |

|                  | 7.2.   | Trabaj  | o Futuro                                     |   |  |   |   | 80         |

| $\mathbf{G}$     | losari | o de a  | crónimos                                     |   |  |   |   | 81         |

| Bi               | bliog  | rafía   |                                              |   |  |   |   | 83         |

| $\mathbf{A}_1$   | nexo:  | FPGA    | A.                                           |   |  |   |   | Ι          |

| Aı               | nexo:  | Mode    | lo VHDL Convertidor Boost Elevador           |   |  |   |   | IX         |

| $\mathbf{A}_{1}$ | nexo:  | Mode    | lo VHDL ADC                                  |   |  |   |   | ΧI         |

| Aı               | nexo:  | Códig   | o VHDL Regulador Lazo de Tensión Real        |   |  |   | X | III        |

| Aı               | nexo:  | Códig   | o VHDL Regulador Lazo de Tensión             |   |  |   |   | хv         |

| Aı               | nexo:  | Códig   | o VHDL Regulador Doble Lazo                  |   |  |   | 3 | ΚIX        |

|                  |        |         |                                              |   |  |   |   |            |

Anexo: Codigo VHDL Selec xxv

Presupuesto xxvII

Pliego de condiciones xxIX

# Índice de figuras

| 1.1.  | Cronograma                                                                                     | 2  |

|-------|------------------------------------------------------------------------------------------------|----|

| 1.2.  | Diagrama de Bloques de la Fuente Lineal                                                        | 4  |

| 1.3.  | Diagrama de Bloques de la Fuente Conmutada                                                     | 4  |

| 1.4.  | Topologías de Convertidores Conmutados                                                         | 5  |

| 1.5.  | Modulación PWM: Onda Cuadrada                                                                  | 7  |

| 1.6.  | Lazo Abierto                                                                                   | 8  |

| 1.7.  | Lazo Cerrado                                                                                   | 8  |

| 1.8.  | Control PWM por muestra de tensión                                                             | 9  |

| 1.9.  | Control PWM por muestra de corriente                                                           | 9  |

| 1.10. | Control de Doble Lazo                                                                          | 10 |

| 1.11. | Triángulo de Potencias                                                                         | 11 |

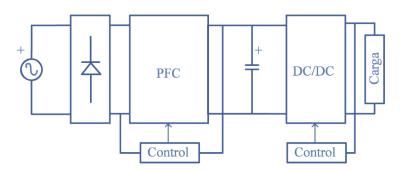

| 1.12. | Diagrama Rectificador                                                                          | 12 |

| 1.13. | Circuitos Pasivos                                                                              | 13 |

| 1.14. | Convertidor AC/DC de Doble Etapa $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$       | 13 |

| 1.15. | Boost Elevador                                                                                 | 14 |

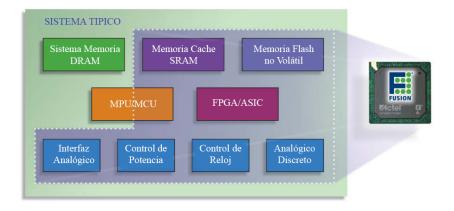

| 2.1.  | Sistema Típico                                                                                 | 17 |

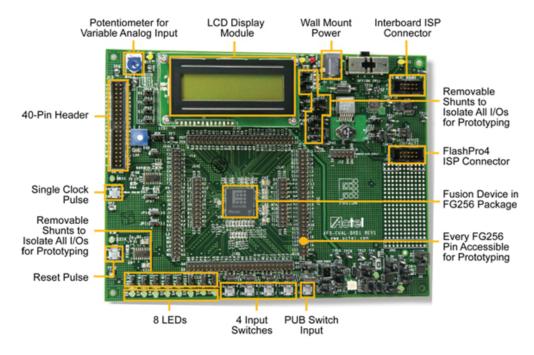

| 2.2.  | Fusion Starter Kit                                                                             | 18 |

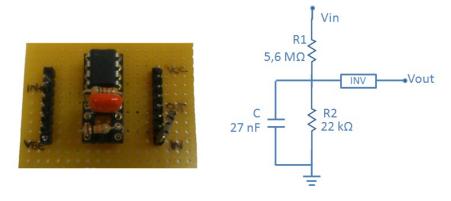

| 2.3.  | $\operatorname{Reloj}...................$                                                      | 20 |

| 2.4.  | Diagrama Bloques ADC                                                                           | 20 |

| 2.5.  | Diagrama SAR del ADC                                                                           | 21 |

| 2.6.  | Diagrama de bloques del multiplexor de entrada del ADC                                         | 22 |

| 2.7.  | Sisotool                                                                                       | 24 |

| 2.8.  | $ModelSim \ \ldots \ $ | 25 |

| 2.9.  | ProjectFlowWindow                                                                              | 26 |

| 2.10. | Analog System Builder                                                                          | 27 |

| 2.11. | Analog system Buider Advanced Option Dialog Box                                                | 28 |

| 2.12. | Interfaz Gráfica FlashPro                                                                      | 29 |

| 3 1   | Boost Elevador                                                                                 | 39 |

| 3.2.  | Formas de onda en MCC                                                                      | 33 |

|-------|--------------------------------------------------------------------------------------------|----|

| 3.3.  | Formas de onda en MCD                                                                      | 35 |

| 3.4.  | Rizado en Tensión de Salida                                                                | 36 |

| 3.5.  | Boost Elevador                                                                             | 36 |

| 3.6.  | Divisores de Tensión de Entrada y Salida                                                   | 37 |

| 3.7.  | Divisor de Tensión para la Medición de la Corriente de Entrada                             | 37 |

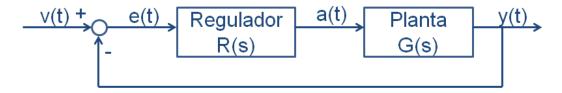

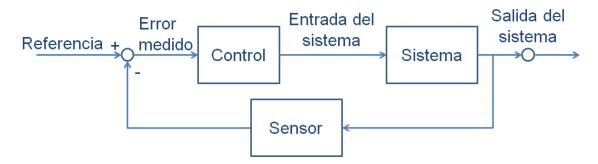

| 4.1.  | Lazo Cerrado                                                                               | 39 |

| 4.2.  | Función de Transferencia                                                                   | 41 |

| 4.3.  | Control Realimentado                                                                       | 43 |

| 4.4.  | Acciones de Control P, PI y PD                                                             | 44 |

| 4.5.  | Ciclos de trabajo distintos para mismo periodo                                             | 45 |

| 4.6.  | Lazo de Tensión                                                                            | 46 |

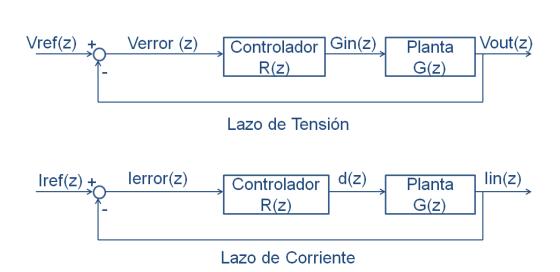

| 4.7.  | Doble Lazo                                                                                 | 46 |

| 4.8.  | Formas de onda para $V_i, I_L, P_i, P_o, V_o$                                              | 47 |

| 4.9.  | Tensión Rectificada                                                                        | 47 |

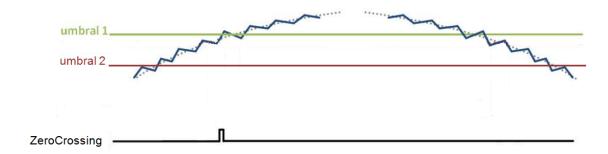

| 4.10. | . Detección de paso por cero                                                               | 48 |

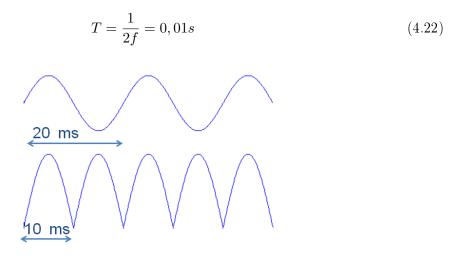

| 4.11. | . Frecuencia de la Red normal vs frecuencia rectificada                                    | 48 |

| 4.12. | . Regulador de lazo de tensión                                                             | 50 |

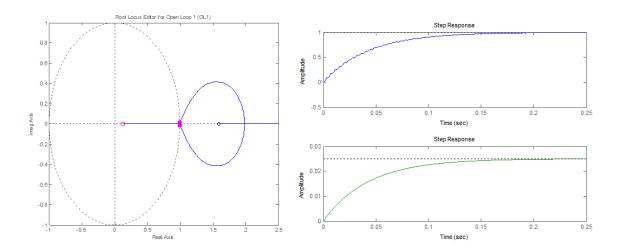

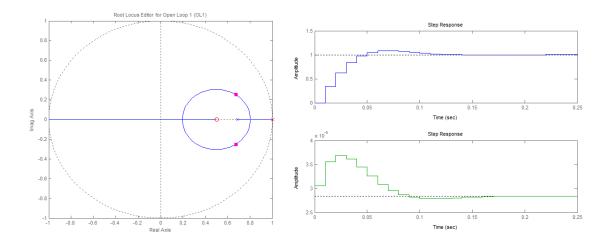

| 4.13. | . Respuesta Controlador Lazo de Tensión                                                    | 51 |

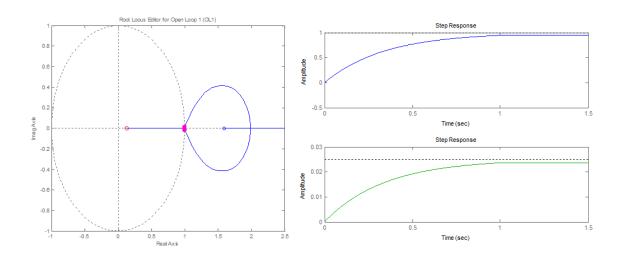

| 4.14. | . Respuesta Controlador Lazo de Tensión - CT1                                              | 52 |

| 4.15. | . Reguladores de lazo de tensión y corriente                                               | 54 |

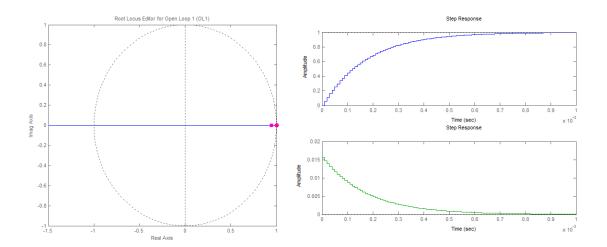

| 4.16. | . Respuesta Controlador Lazo de Tensión                                                    | 55 |

| 4.17. | . Respuesta Controlador Lazo de Corriente                                                  | 55 |

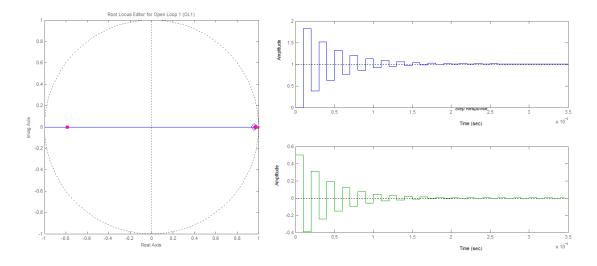

| 4.18. | . Respuesta Controlador Lazo de Corriente - C1                                             | 56 |

| 4.19. | . Respuesta Controlador Lazo de Corriente - C2                                             | 57 |

| 4.20. | . Respuesta Controlador Lazo de Corriente - C3                                             | 57 |

| 4.21. | Formato QX.Y                                                                               | 58 |

| 4.22. | . Suma Formato QX.Y                                                                        | 58 |

| 4.23. | . Producto Formato QX.Y                                                                    | 59 |

| 4.24. | . Generación de la señal PWM                                                               | 60 |

| 5.1.  | Sincronización del canal y resultado del ADC                                               | 63 |

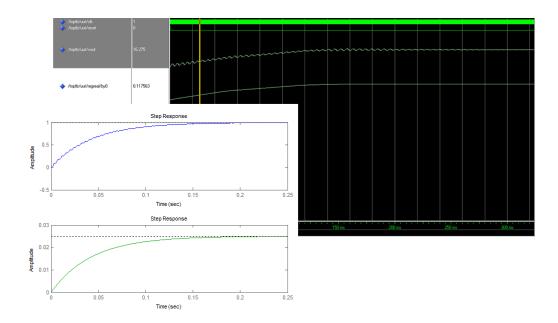

| 5.2.  | Resultados Sisotool vs ModelSim                                                            | 64 |

| 5.3.  | Comparativa Regulador real VS std_logic_vector                                             | 64 |

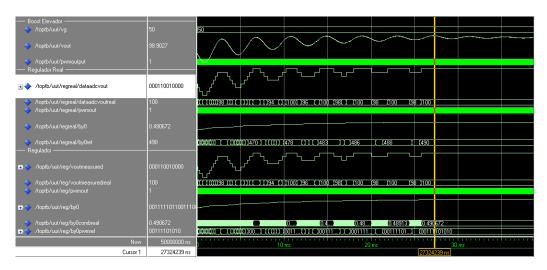

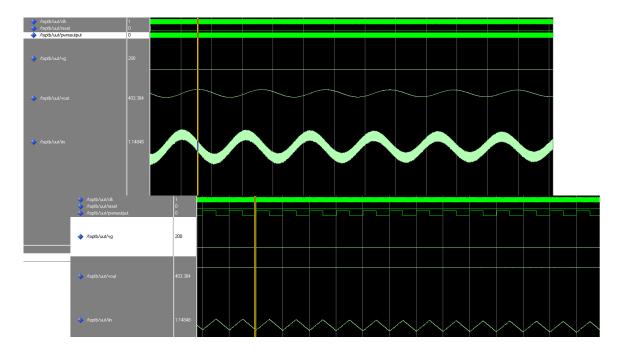

| 5.4.  | Simulación controladores utilizados D= $50\%$                                              | 66 |

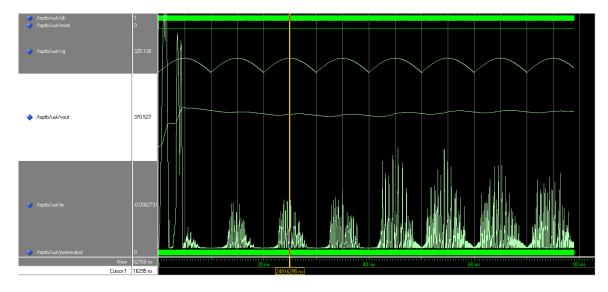

| 5.5.  | Simulación Lazo Cerrado - Tiempo de adquisición y conversión ADC = 3,33 $\mu \mathrm{s}$ . | 66 |

| 5.6.  | ASB - Secuencia de muestreo                                                                 | 67 |

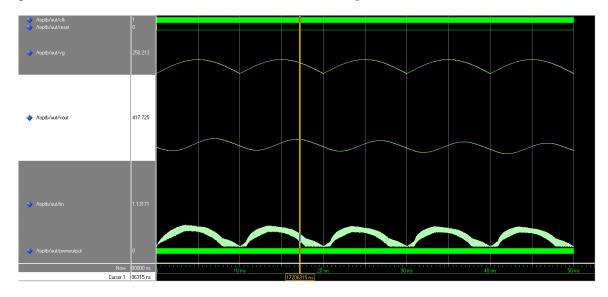

|-------|---------------------------------------------------------------------------------------------|----|

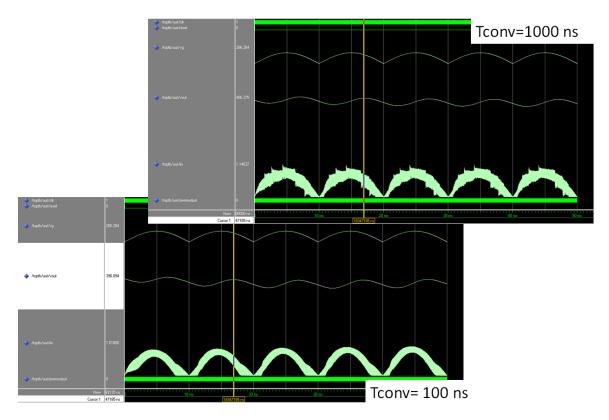

| 5.7.  | Simulación Lazo Cerrado - Tiempo de adquisición y conversión ADC = 36,15 $\mu \mathrm{s}$ . | 67 |

| 5.8.  | Simulación Lazo Cerrado - Tiempo de adquisición y conversión ADC = $1000/100$ ns            | 68 |

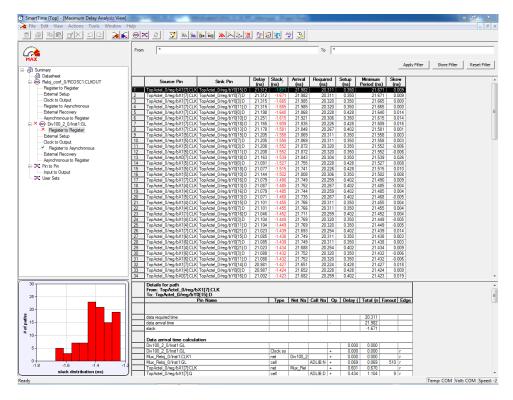

| 6.1.  | SmartTime                                                                                   | 70 |

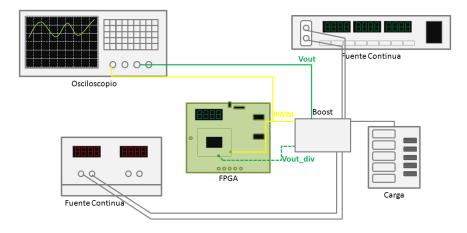

| 6.2.  | Esquema Conexionado: Control de Lazo de Tensión                                             | 70 |

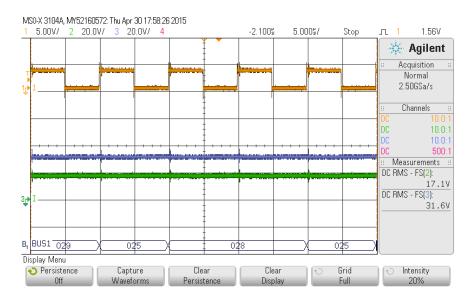

| 6.3.  | Control Lazo de Tensión: Lazo Abierto                                                       | 71 |

| 6.4.  | Control Lazo de Tensión: Lazo Abierto                                                       | 72 |

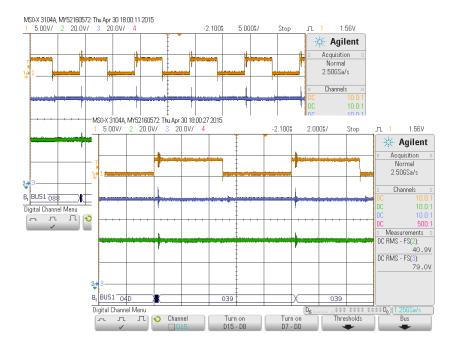

| 6.5.  | Control Lazo de Tensión: Lazo Cerrado                                                       | 72 |

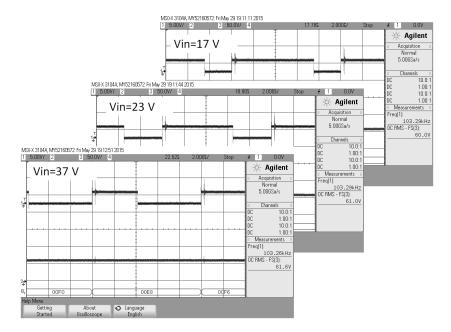

| 6.6.  | Simulación Lazo Cerrado - Vref=40 V; Vin=15 V; R=200 $\Omega$ ;                             | 73 |

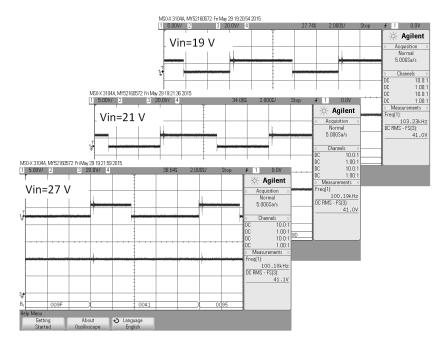

| 6.7.  | Simulación Lazo Cerrado - Vref=40 V; Vin=19;21;27 V; R=200 $\Omega;$                        | 73 |

| 6.8.  | Simulación Lazo Cerrado - Vref=40 V; Vin=15 V; R=500 $\Omega$ ;                             | 74 |

| 6.9.  | Simulación Lazo Cerrado - Vref=40 V; Vin=19;21;27 V; R=500 $\Omega;$                        | 74 |

| 6.10. | . Simulación Lazo Cerrado - Vref=60 V; Vin=17 V; R=200 $\Omega$ ;                           | 75 |

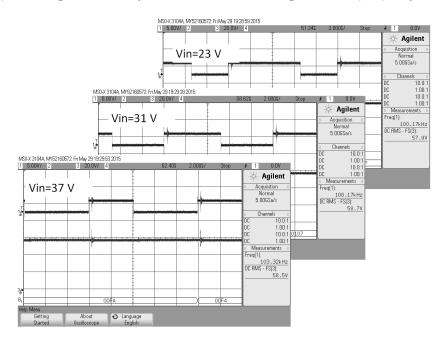

| 6.11. | . Simulación Lazo Cerrado - Vref=60 V; Vin=23;31;37 V; R=200 $\Omega;$                      | 75 |

| 6.12. | . Simulación Lazo Cerrado - Vref=60 V; Vin=17;23;37 V; R=500 $\Omega$ ;                     | 76 |

| 6.13. | Esquema Conexionado Control de Doble Lazo                                                   | 76 |

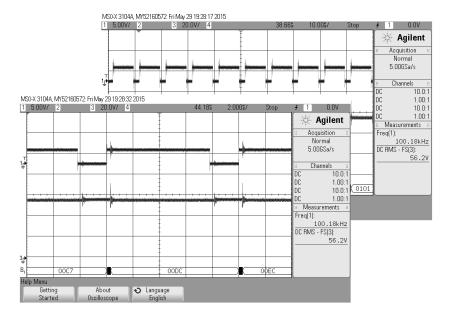

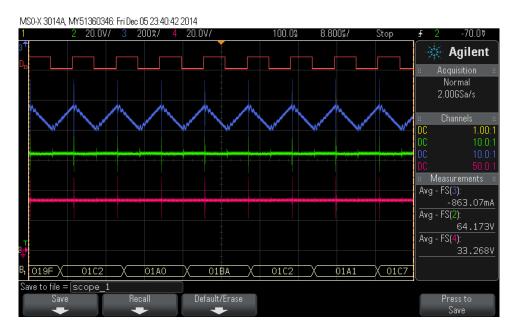

| 6.14. | . Control Doble Lazo: Lazo Abierto                                                          | 77 |

| 6.15. | . Control Doble Lazo: Lazo Cerrado                                                          | 78 |

$Control\ digital\ de\ convertidor\ conmutado\ mediante\ FPGA\ mixta\ anal\'ogica/digital$

1

# Introducción y Estado del Arte

En este capítulo serán expuestos los antecedentes históricos que han contribuido al desarrollo de lo que hoy conocemos como electrónica junto al estado del arte actual de los controladores digitales. Como el propio nombre del proyecto indica, "Control digital de convertidor conmutado mediante FPGA mixta analógica/digital", el control digital de convertidores conmutados será el tema central del presente proyecto fin de carrera.

Dentro del estado del arte actual se incluye el estado de las fuentes de alimentación, lineales y conmutadas, para después introducir la modulación por ancho de pulso, técnica utilizada para la regulación de la tensión de salida del convertidor conmutado, y los tipos de lazos de control, abierto o cerrado. Finalmente se introduce el factor de potencia, indicador del correcto aprovechamiento de la energía eléctrica y las soluciones para la mejora de este factor.

## 1.1. Antecedentes Históricos

Desde principios del siglo XVII, la electricidad ha sido materia de interés científico. Desde ese momento, los experimentos llevados a cabo por diferentes científicos en torno a los fenómenos eléctricos y electromagnéticos, fueron asentando las bases para lo que poco tiempo después sería una nueva especialidad, primero la física y seguidamente la ingeniería. Sin embargo, las investigaciones dentro de la ingeniería eléctrica no empezaron a intensificarse hasta el siglo XIX.

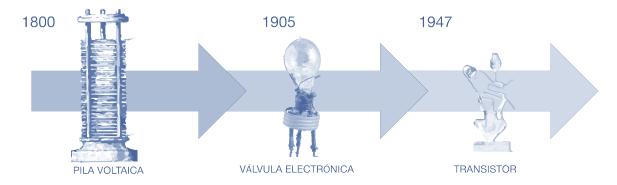

El invento de la pila voltaica en 1800 hizo posible el desarrollo de los primeros circuitos eléctricos, es decir, conjunto de elementos que unidos entre sí permiten una circulación de electrones o lo que es lo mismo una corriente eléctrica. La primera aplicación de estos circuitos fue la iluminación eléctrica.

A continuación, en 1884 Thomas Edison detectó el fenómeno termoiónico por el cual los electrones que se encuentran en la superficie de los metales pueden llegar a desprenderse de la misma como consecuencia de un aumento en su velocidad producida por un aumento de temperatura.

Thomas Edison no pudo darse cuenta de la importancia de su descubrimiento y fue John Ambrose Flemming quien en 1905 descubrió que colocando dentro de la bombilla incandescente otro electrodo independiente, y algo alejado del filamento, se establecía una circulación de corriente eléctrica desde el filamento (cátodo) hacia el nuevo electrodo (ánodo). Fue así como Flemming

Figura 1.1: Cronograma

inventó la primera válvula electrónica, lo que dio lugar al nacimiento de la ingeniería electrónica y abrió el camino a los posteriores avances de la electrónica moderna. Es importante destacar que todos estos descubrimientos originaron el comienzo del control del paso de corriente.

La válvula presentaba inconvenientes entre los cuales cabe destacar el elevado consumo energético y la escasa fiabilidad debida a sus elevadas temperaturas de funcionamiento, lo que con el paso del tiempo ocasionó que terminaran siendo sustituidos por los transistores [1] tal y como se observa en la figura 1.1. Fue en 1947 cuando William Sockley, John Bardeen y Walter Brattain construyeron el primer transistor respondiendo a la necesidad técnica de hacer llamadas telefónicas a larga distancia. Es por ello que el transistor es considerado uno de los mayores desarrollos tecnológicos del siglo XX.

Los transistores permitían cumplir con las mismas funciones que las válvulas a la vez que utilizaban menores cantidades de energía y se trataba de dispositivos mucho más versátiles, económicos y pequeños.

En los años posteriores a la invención del primer transistor se siguieron produciendo adelantos en este campo: se inventaron distintos tipos de transistores, se emplearon distintos materiales y se logró la integración de un gran número de transistores en un oblea de silicio. Este último adelanto dio lugar a la creación del circuito integrado [2] en 1958 por Kilby. El circuito integrado disminuía la complejidad en el diseño de circuitos electrónicos al aumentar el número de componentes como consecuencia de las malas conexiones, además de propiciar un reducción de las dimensiones, el peso y el coste en relación al número de elementos integrados.

A partir de la comercialización de los circuitos integrados en 1961, la densidad de transistores en un mismo espacio se ha duplicado cada 24 meses. Esta tendencia se ha mantenido hasta la actualidad y es conocida como ley de Moore [3].

Hoy en día, la industria de los semiconductores está sacando al mercado circuitos integrados con transistores de 22 nanómetros [4] [5]. Esto permite que podamos encontrar 4,31 billones de transistores en un único procesador como sucede en el caso del procesador E7 - 8857 de Intel. Debido a que seguir decrementando el tamaño de los transistores podría suponer un coste de fabricación superior al de venta, los fabricantes están comenzando a plantarse en los tamaños actuales y buscar alternativas como por ejemplo en los materiales [6] [7].

Actualmente existen distintas tecnologías para la implementación de circuitos integrados digitales. Aunque con los ASICs [8] [9], circuitos integrados de aplicación específica, se obtienen velocidades superiores al poder optimizar al máximo el diseño y un menor consumo [10] [11], no resultan beneficiosos para etapas de prototipado. Por el contrario, las FPGAs [12] [13] son dispositivos semiconductores que contienen bloques de lógica cuya interconexión y funcionalidad puede ser reprogramada mediante un lenguaje de descripción especializado. La lógica programable puede reproducir desde funciones tan sencillas como las llevadas a cabo por una puerta

lógica o un sistema combinacional hasta complejos sistemas en un chip.

Dada la versatilidad, flexibilidad y por ser fácilmente programable, el presente proyecto se ha decantado por la utilización de una plataforma hardware de desarrollo que contiene señales mixtas analógica/digital de Microsemi [14] que será detallada en el capítulo 2. Gracias a las capacidades de la FPGA incluida en la plataforma a utilizar, es posible llevar a cabo la captura de señales analógicas mediante un ADC integrado y realizar el procesado con la lógica programable, lo cual permitirá la regulación de la tensión de salida de un convertidor boost elevador.

A continuación, se presenta un estudio del estado del arte de la fuentes de alimentación al encontrarse el convertidor boost elevador dentro de la categoría de las fuentes de alimentación conmutadas. Posteriormente, nos centraremos en los controladores, sistemas por medio de los cuales es posible gobernar una señal de salida a través de una señal de entrada. Por último, se tratará el factor de potencia, indicador que permite describir la cantidad de energía transformada en potencia en las fuentes de alimentación. El factor de potencia se mueve entre valores de 0 y 1, un mayor factor de potencia permite la reducción del consumo energía y por tanto la reducción de la factura eléctrica [15].

## 1.2. Estado del Arte

Cualquiera de los dispositivos o circuitos electrónicos mencionados anteriormente y los existentes en la actualidad, tienen una cosa en común: la dependencia de la energía para poder funcionar. La energía, la cual puede obtenerse de diversas fuentes como por ejemplo a través de una pila, una batería o de la red eléctrica, tiene un inconveniente, no cuenta con un formato unificado, es decir, podemos encontrarla como corriente continua o corriente alterna.

Actualmente, en España, la red eléctrica viene dada por corriente alterna de 230 V. Esto, en muchos casos, no satisface las necesidades de los diferentes dispositivos conectados a la red eléctrica lo que hace necesario una serie de elementos que permitan transformar la energía de entrada a una de salida con los valores adecuados. Estos elementos, denominados fuentes de alimentación, serán detallados a continuación.

## 1.2.1. Fuentes de alimentación

En la actualidad las fuentes de alimentación [16] se pueden clasificar en lineales y conmutadas. Cada una de estas fuentes cuenta con sus propias características, ventajas y inconvenientes. Por ello, la utilización de una tipología en concreto dependerá de su uso final y los requerimientos de estabilidad y rendimiento de la carga a alimentar.

#### Fuentes Lineales

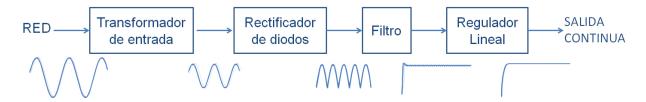

Las fuentes de alimentación lineales, las primeras en desarrollarse, utilizan un transformador para aumentar o disminuir el voltaje de la red eléctrica y poder adecuarlo así a las necesidades del circuito. Estas fuentes, a grandes rasgos quedan definidas por los bloques incluidos en la figura 1.2.

El transformador de entrada modifica los niveles de tensión alterna a los requeridos por el circuito a alimentar aumentando o reduciendo la tensión de red a otra tensión más adecuada para ser tratada.

A continuación, el rectificador es el encargado de convertir la tensión alterna que sale del transformador en tensión continua. Para realizar esta conversión se utilizan diodos, los cuales

Figura 1.2: Diagrama de Bloques de la Fuente Lineal

Figura 1.3: Diagrama de Bloques de la Fuente Conmutada

conducen cuando la tensión de su ánodo es mayor que la de su cátodo. La tensión de salida de un rectificador tiene forma de pulsos, es decir, en un ciclo de salida completo la tensión aumenta de cero a un valor de pico, para caer después de nuevo a cero.

Debido a que la mayor parte de circuitos electrónicos precisan de una tensión constante, similar a la que produce una batería, después del rectificador es necesario el empleo de filtro para la obtención de una tensión rectificada. El tipo más común de filtro es el condensador a la entrada del circuito ya que se trata de un elemento que se opone a las variaciones bruscas de la tensión que se le aplica. Sin embargo, en algunos casos puede no ser suficiente y es necesaria la utilización de algunos componentes adicionales.

Por último, el regulador lineal o estabilizador es el circuito encargado de reducir el rizado que puede llevar asociada la tensión proporcionando así una tensión de salida adecuada.

Uno de los principales inconvenientes de las fuentes lineales es su gran tamaño, además de disipar gran parte de la energía en forma de calor. Esto, unido a algunas de las necesidades de la carrera aeroespacial como la reducción de peso y consumo, desencadenó el primer desarrollo de las fuentes de alimentación conmutadas en los años 60, las cuales producen una mayor eficiencia energética y un menor calentamiento además de la reducción en tamaño, peso y coste.

#### Fuentes Conmutadas o Convertidores

A diferencia de las fuentes lineales, las fuentes conmutadas son convertidores continua/continua, por lo que la red debe ser previamente rectificada y filtrada con una amplitud de rizado aceptable. Estas fuentes se componen de circuitos relativamente complejos, aunque siempre es posible diferenciar cuatro bloques básicos identificados en las figura 1.3.

El primer bloque rectifica y filtra la tensión alterna de entrada convirtiéndola en una continua pulsante. A continuación, el segundo bloque se encarga de convertir esa continua en una onda cuadrada de alta frecuencia.

El tercer bloque rectifica y filtra la salida de alta frecuencia del bloque anterior, entregando así una corriente continua pura.

Por último, el cuarto bloque se encarga de regular la oscilación del segundo bloque. Este bloque consiste en un oscilador de frecuencia fija, una tensión de referencia, un comparador de tensión y un modulador de ancho de pulso, Pulse Width Modulation (PWM). El modulador

recibe el pulso del oscilador y modifica su ciclo de trabajo según la señal del comparador, el cual coteja la tensión continua de salida del tercer bloque con la tensión de referencia.

En sus principios las fuentes conmutadas eran una tecnología muy cara y desconocida, pero el abaratamiento de la electrónica y la miniaturización ha conseguido el desarrollo de las mismas con una mayor estabilidad, seguridad, eficiencia y un precio similar a las fuentes lineales.

Hoy en día se siguen utilizando las fuentes lineales ya que generan menor ruido y rizado, tienen un bajo coste y por su simplicidad, son más inmunes a las radiaciones electromagnéticas.

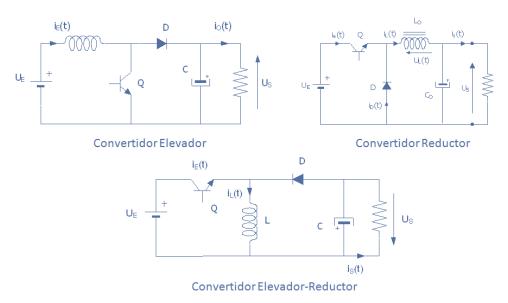

#### Topologías de Convertidores Conmutados

Como ya se ha mencionado anteriormente, los convertidores conmutados transforman una tensión de entrada continua en una de salida también continua de diferente nivel. Aunque existen diferentes topologías de convertidores, a continuación se detallan los más frecuentes:

- Elevador o Boost: La tensión de salida es mayor que la de entrada.

- Reductor o Buck: La tensión de salida es menor que la de entrada.

- Elevador-Reductor o Boost-Buck: La tensión de salida puede ser mayor o menor pero invertida.

Todos ellos cuentan con un funcionamiento básico consistente en el almacenamiento temporal de energía y la cesión de esta tras un periodo de tiempo que determinará la cantidad de energía cedida a la carga.

A continuación, en la figura 1.4 se pueden observar los esquemas de cada una de las tipologías mencionadas. Aunque todos los esquemas cuentan con los mismos elementos, la disposición de estos varía en función de la topología.

Figura 1.4: Topologías de Convertidores Conmutados

#### 1.2.2. Sistemas de Control

Los métodos de análisis de sistemas y diseño de los controladores [17] [18] [19] han evolucionado del mismo modo que la mayoría de las herramientas utilizadas en ingeniería. Es por ello que en los últimos años estos progresos han permitido que las investigaciones y aplicaciones en la teoría de control hayan pasado de utilizar una implementación analógica a una implementación digital.

En concreto, un sistema de control puede definirse como un sistema que trata de gobernar un cierto proceso físico mediante la generación de una señal de salida a partir de una señal de entrada. La finalidad de un sistema de control es conseguir, mediante la manipulación de las variables de control, un dominio sobre las variables de salida, de modo que estas alcancen unos valores prefijados.

Mientras que en un esquema analógico todas las variables son función de un tiempo continuo, las variables de los esquemas digitales dependen de instantes determinados, es decir, de un tiempo discreto.

La ventaja de un control analógico es el gran ancho de banda con el que trabaja, consecuencia del uso de señales en tiempo real, lo que es equivalente a frecuencia de muestreo infinita de modo que el efecto del controlador está presente en todo momento. Sin embargo, el incremento en la utilización de los sistemas digitales frente a los analógicos con el paso de los años se debe a las ventajas que estos proporcionan.

Para poder entender el aumento del uso de los controles digitales, a continuación se pueden encontrar las ventajas más destacas de estos sistemas [17]:

- Menor susceptibilidad al envejecimiento y a las variaciones de las condiciones ambientales.

- Menor sensibilidad al ruido y a las perturbaciones.

- Mayor fiabilidad ya que poseen una mejor sensibilidad frente a la variación de parámetros.

- Posibilidad de generar algoritmos de control altamente complejos.

- Facilidad de modificación de los algoritmos de control ya que un cambio en el control no requiere cambios en el hardware.

- Posibilidad de uso del ordenador para tareas adicionales como reconocimiento de imágenes, conversión de coordenadas, etc.

- Reprogramación.

- Menor peso y tamaño.

Aunque tampoco se debe olvidar que los sistemas de control digital también presentan desventajas frente a los sistemas analógicos como por ejemplo:

- Necesidad de la utilización de conversores analógico/digital que permitan discretizar las señales y conversores digital/analógico para devolver las señales a un tiempo continuo.

- Limitaciones en la velocidad de cálculo y en la resolución de la señal debido a la longitud de la palabra finita del procesador digital en contraste con los controladores analógicos que trabajan en tiempo real y tienen una resolución teóricamente infinita.

- Limitación en la velocidad provocada por retrasos en el lazo de control, los cuales pueden provocar inestabilidad en el sistema.

- Precio.

En lo referente a los sistemas de control digital, existen múltiples criterios de clasificación, pero en este caso nos centraremos en la estrategia de control que siguen, es decir, lazo abierto o lazo cerrado, ya que el presente proyecto fin de carrera tiene como objetivo la utilización de un control digital de lazo cerrado para la regulación de la tensión de salida de un conversor alterna/continua.

#### Modulación por Ancho de Pulso (PWM)

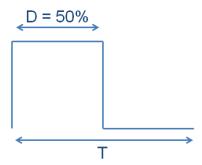

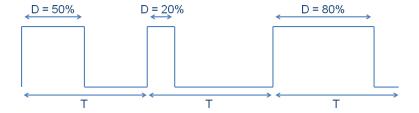

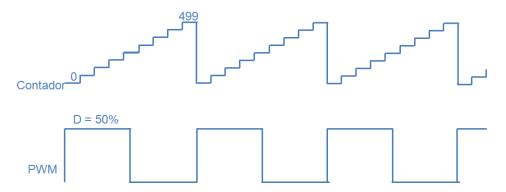

La modulación por ancho de pulso o PWM [20] de una señal o fuente de energía es una técnica en la que se modifica el ciclo de trabajo de una señal periódica, ya sea para codificar la información de una transmisión o para controlar la energía entregada a una carga o dispositivo eléctrico.

En la actualidad es posible encontrar modulación por ancho de pulso incluida en circuitos funcionales que tienen como objetivo el control de fuentes conmutadas, motores, elementos termoeléctricos, etc.

Se denomina ciclo de trabajo de la señal periódica a la proporción de tiempo en alto a intervalos regulares o periódicos de tiempo. El ciclo de trabajo queda expresado entonces por:

$$D = \frac{t_{on}}{T} \tag{1.1}$$

donde:

- D es el ciclo de trabajo

- ullet  $t_{on}$  es el tiempo en alto o ancho de pulso

- T es el periodo de la señal

El ciclo de trabajo se expresa en tanto por ciento. Por ello,  $D=100\,\%$  corresponde con un periodo completo en estado alto.

Para el caso concreto bajo estudio, controladores digitales, el buen funcionamiento de la modulación por ancho de pulso se debe a su naturaleza de encendido/apagado que permite establecer de manera sencilla el ciclo de trabajo deseado.

Figura 1.5: Modulación PWM: Onda Cuadrada

#### Lazo Abierto

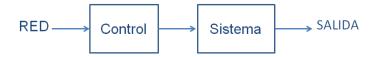

Los sistemas de control en lazo abierto (ver figura 1.6) son aquellos en los que la variable de salida no tiene efecto sobre la acción o variable de control. Este sistema suele aparecer en dispositivos con control secuencial, en el que no hay una regulación de variables sino que se realizan una serie de operaciones de una manera determinada.

La estrategia de control lazo abierto puede compensar los retrasos inherentes del sistema anticipándose a las necesidades del usuario, sin embargo, esto generalmente es insuficiente debido a los errores del modelo y a los errores en la estimación de las perturbaciones.

Figura 1.6: Lazo Abierto

#### Lazo Cerrado

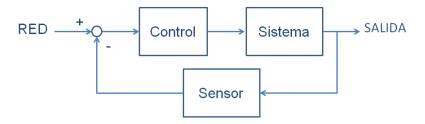

Los sistemas de control en lazo cerrado (ver figura 1.7) son aquellos en los que la señal de salida del sistema tiene efecto directo sobre la acción o variable de control.

Para aquellos casos en los que se utiliza una estrategia de control de lazo cerrado, las perturbaciones, aunque sean desconocidas, son consideradas indirectamente mediante sus efectos sobre las variables de salida. Este tipo de estrategia de control puede aplicarse sea cual sea la variable controlada. Por ello, la gran mayoría de los sistemas de control que se desarrollan en la actualidad son en lazo cerrado.

Figura 1.7: Lazo Cerrado

En el caso particular del control digital, independientemente del tipo de convertidor utilizado, la señal de salida tiene una dependencia directa con la señal de ciclo de trabajo. Dependiendo de la frecuencia de conmutación de esta señal es posible encontrar:

- Sistemas de control a frecuencia fija.

- Sistemas de control a frecuencia variable.

Los sistemas de control a frecuencia fija son aquellos sistemas donde la frecuencia de conmutación se mantiene constante, variando únicamente el tiempo de conducción de la señal de ciclo de trabajo. Por el contrario, los sistemas de control a frecuencia variable pueden realizarse a su vez de dos formas, según el tiempo de conducción sea fijo o variable.

El sistema de control a frecuencia fija, el utilizado en el presente proyecto fin de carrera, consiste en cambiar la señal de error obtenida de la comparación de la señal de salida y la señal de referencia, con otra señal de frecuencia fija procedente de un oscilador que determinar la frecuencia de funcionamiento del sistema. El resultado de esta combinación es otra señal, cuya frecuencia queda fijada por el oscilador y cuyo ciclo de trabajo es función de la señal de salida. Se dice entonces que la señal obtenida está modulado mediante Modulación por Ancho de Pulso (PWM).

A su vez, los sistemas de control en lazo cerrado pueden categorizarse en:

- Sistema de control PWM por muestra de tensión.

- Sistemas de control PWM por muestra de corriente.

- Sistema de control PWM por muestra combinada tensión-corriente.

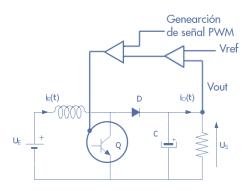

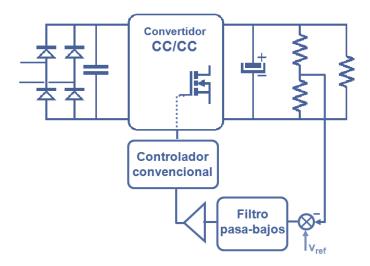

#### Sistema de Control PWM por muestra de tensión

El funcionamiento de este sistema, también conocido por Control de Tensión, se basa en la obtención de una muestra directamente de la salida del circuito para ser comparada posteriormente con una tensión de referencia que contiene la tensión de salida deseada como se puede observar en la figura 1.8. De esta comparación se obtiene una señal de error capaz de generar la señal de PWM que actúa sobre el conmutador obligando a este a variar su ciclo de trabajo.

En estos sistemas, la regulación de la tensión de salida no es inmediata y depende de la magnitud de la variación, por tanto, es posible que el circuito necesite varios ciclos de conmutación para llevar a la señal de salida al nivel deseado.

Figura 1.8: Control PWM por muestra de tensión

#### Sistemas de control PWM por muestra de corriente

Los sistemas de control PWM por muestra de corriente, también conocidos como Control de Corriente, toman normalmente la muestra de corriente directamente sobre el inductor ya que esta es la zona donde se producen las máximas variaciones de la corriente por la carga. Este sistema estabiliza al circuito frente a las posible variaciones de la señal de entrada.

Del mismo modo que sucede en el Control de Tensión, la muestra de corriente es comparada con una corriente de referencia dando lugar a una señal de error encargada de la generación de la señal de conmutación que actúa sobre el conmutador (ver figura 1.9).

Figura 1.9: Control PWM por muestra de corriente

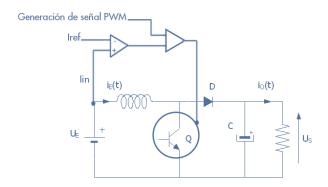

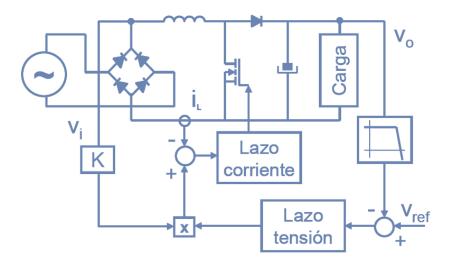

#### Sistema de control PWM por muestra combinada tensión-corriente

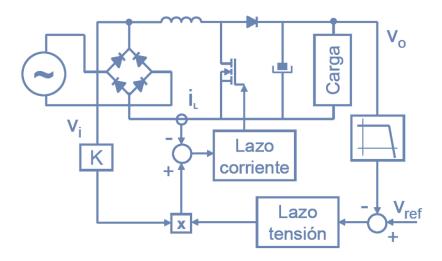

Este sistema llevan a cabo el control por medio de una etapa que contiene un doble lazo, mientras un lazo regula la corriente de entrada, el otro regula la tensión de salida.

El lazo de tensión, compara la tensión de salida con una tensión de referencia generando así

la señal de error. Esta señal de error será utilizada como referencia en el lazo de corriente, por lo que será comparada con la corriente de entrada de modo que la salida tras la comparación actuará sobre el ciclo de trabajo utilizado como conmutador.

El lazo de corriente se encarga de mantener la corriente de entrada en el valor deseado. La corriente de entrada deberá ser proporcional a la tensión de entrada y conseguir así la corrección del factor de potencia.

A continuación, en la figura 1.10 se puede observar el esquema de doble lazo analizado.

Figura 1.10: Control de Doble Lazo

Este sistema de control se encuentra dentro de las soluciones activas para el corrector de factor de potencia descritas en el apartado 1.2.3.

## 1.2.3. Factor de Potencia

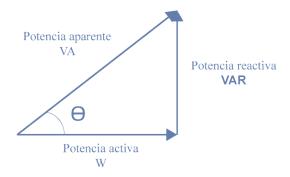

El Factor de Potencia [20] [21] es un indicador cualitativo y cuantitativo del correcto aprovechamiento de la energía eléctrica aunque también puede describirse como el término utilizado para describir la cantidad de energía eléctrica convertida en trabajo.

La medición de potencia en corriente alterna es más complicada que la de corriente continua debido al efecto de las bobinas y condensadores, por ello en cualquier circuito de corriente alterna aparecen estos tres parámetros: inductancia, capacitancia y resistencia en una variedad de combinaciones.

En circuitos puramente resistivos la tensión está en fase con la corriente. Algunos ejemplos de estos artefactos son lámparas incandescentes, planchas, estufas eléctricas, etc. en los cuales la totalidad de la energía se transforma en energía lumínica o calorífica, algo que no sucede en los circuitos inductivos o capacitivos donde la tensión y la corriente están desfasadas 90° una respecto a la otra.

En un circuito puramente inductivo la corriente está atrasada 90° respecto de la tensión mientras que en un circuito puramente capacitivo la corriente va adelantada 90° respecto de la tensión. Estos circuitos además del consumo de la potencia activa que suministra la fuente consumen también una potencia reactiva la cual no proporciona ningún tipo de trabajo útil, sino corriente que circula por la red (con sus pérdidas) sin entregar potencia a la carga.

La potencia activa es aquella que consumen los aparatos conectados a la red eléctrica, la cual se transforma en forma de calor o trabajo y se corresponde con la energía útil o potencia

activa o simplemente potencia. Sin embargo, la potencia reactiva es aquella que aparece en motores, transformadores y en general todos los dispositivos eléctricos que hacen uso del efecto de un campo electromagnético, donde además de requerir una potencia activa para efectuar el trabajo útil es necesaria una potencia reactiva para la generación del campo magnético, la cual no produce ningún trabajo. La potencia reactiva está 90° desfasada de la potencia activa.

Por último, la potencia aparente, es aquella que resulta de considerar la tensión aplicada al consumo de la corriente que éste demanda, o lo que es lo mismo la suma de los vectores de la potencia activa y la potencia reactiva (ver figura 1.11).

Figura 1.11: Triángulo de Potencias

En concreto, el Factor de potencia es la relación entre las potencias activa y aparente si las corrientes y es son señales sinusoidales. Si estas son señales perfectamente sinusoidales el factor de potencia será igual al cos  $\theta$ , o bien, al coseno del ángulo que forman los fasores de la corriente y la tensión, designándose en este caso como cos  $\theta$  el valor de dicho ángulo.

Hasta los años 70, las cargas conectadas a la red eléctrica eran mayoritariamente lineales, es decir, demandaban corriente en forma de onda sinusoidal. Esto producía que el factor de potencia pudiese ser definido por la siguiente ecuación:

$$PF = \frac{PotenciaActiva}{PotenciaAparente} = \frac{V_{ef}I_{ef}cos\theta}{V_{ef}I_{ef}} = cos\theta$$

(1.2)

A partir de ese momento, el número de cargas no lineales conectadas a la red ha ido aumentando constantemente. Debido a que las cargas no lineales demandan corriente no sinusoidales se produce la introducción de armónicos en la red eléctrica, y por lo tanto, será necesario la obtención de una nueva ecuación de factor de potencia:

$$PF = \frac{PotenciaActiva}{PotenciaAparente} = \frac{V_{ef}I_{ef1}cos\theta}{V_{ef}I_{ef}} = \frac{I_{ef1}cos\theta}{I_{ef}}$$

(1.3)

donde  $I_{ef1}$  se refiere a la corriente eficaz del primer armónico.

La proliferación del número de cargas no lineales conectadas actualmente a la red eléctrica pueden provocar un alto contenido armónico. Si no se hiciese nada para corregir este comportamiento, se podrían llegar a dañar los equipos conectados a la red. Para tratar de solucionar este problema en la medida de lo posible, distintas organizaciones internacionales han elaborado una normativa destinada a reducir el nivel de armónicos introducidos en la red (Norma EN61000-3-2) [22]. Es por ello que las técnicas de Corrección del Factor de Potencia han experimentado un notable desarrollo.

La norma EN 61000-3-2 abarca todos aquellos equipos electrónicos y eléctricos que se conecten a la red pública de baja tensión y cuya corriente es menor o igual que 16 A. El objetivo es

limitar el contenido armónico de la corriente absorbida de la red para lo cual clasifica los equipos en cuatro clases y aplica límites diferentes en función de la clase a la que pertenezca el aparato e incluso de las características de potencia del equipo.

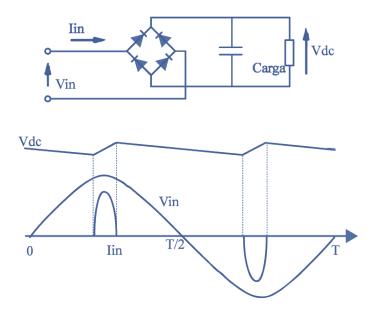

#### Soluciones para la Corrección de Factor de Potencia

Tradicionalmente, para realizar la conversión alterna/continua se empleaba un circuito compuesto por un puente de diodos con un condensador de filtro ya que se trataba de un circuito sencillo, robusto y barato (ver figura 1.12). Debido a que la forma de onda de la corriente absorbida de la red en este tipo de rectificadores se compone de picos de corta duración y elevado valor, tanto positivos como negativos, y que el condensador presenta una tensión continua de valor muy próximo a la tensión de pico de red, sólo se producirá circulación de corriente cuando el valor instantáneo de la tensión de entrada sea mayor que la tensión en el condensador.

Figura 1.12: Diagrama Rectificador

Idealmente, para evitar la circulación de armónicos por la red, la corriente absorbida por los equipos debería ser sinusoidal y para evitar componentes reactivas, la tensión y la corriente debería estar en fase. En el caso del puente de diodos con condensador de filtro la corriente absorbida de la red dista mucho de ser sinusoidal como se muestra en la figura 1.12, por tanto, presenta un contenido armónico muy elevado.

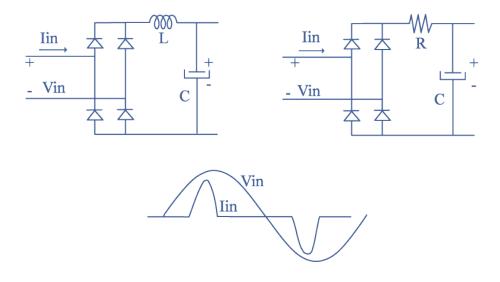

Para cumplir con la Norma EN61000-3-2 [22] no siempre es necesario contar con una corriente de entrada sinusoidal, sino que es posible la utilización de un gran número de circuitos que podemos clasificar en pasivos y activos.

Inicialmente la corrección del factor de potencia utilizó circuitos pasivos los cuales tenían como objetivo principal la corrección del desplazamiento existente entre la tensión y corriente en la red eléctrica. Con el paso del tiempo, además del filtrado armónico producido por la corrección de desplazamiento surgen necesidades adicionales como el control de la tensión y potencia de salida los cuales requieren de la utilización de circuitos activos.

#### Soluciones Pasivas

Las soluciones pasivas (ver figura 1.13) están basadas en la utilización de elementos pasivos los cuales suavizan la corriente de entrada. Estas soluciones añaden elementos reactivos, bobinas

y condensadores, al rectificador para que de esta manera el contenido armónico quede dentro de los límites establecidos por la norma.

Las soluciones pasivas se caracterizan por ser soluciones simples, robustas y baratas, pero presentan el problema de realizarse para unas condiciones de carga determinadas lo que provoca que fuera de estas condiciones la corrección ya no será tan efectiva.

Figura 1.13: Circuitos Pasivos

#### Soluciones Activas

Las soluciones activas son circuitos basados en convertidores DC/DC que consiguen obtener de la red una corriente sinusoidal o cuasi-sinusoidal lo que provoca que nos encontremos ante soluciones más costosas y menos robustas que las pasivas.

Dentro de las soluciones activas es posible encontrar diferentes categorías aunque en esta ocasión serán detallados los convertidores AC/DC de dos etapas.

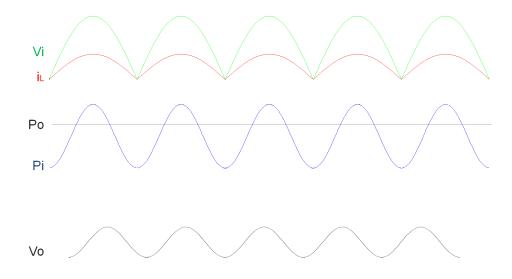

Como se puede observar en la figura 1.14, en los convertidores de dos etapas existe un etapa dedicada a la corrección de factor de potencia y una etapa de conversión DC/DC. En la etapa de corrección de factor de potencia conviven dos lazos, mientras uno obliga a la corriente de entrada a adoptar una forma idéntica a la de la tensión de entrada, así como a permanecer en fase con ella, el segundo lazo regula la tensión en el condensador de almacenamiento. Por último, la segunda etapa, cuenta con un único lazo encargado de la regulación de la tensión de salida.

Figura 1.14: Convertidor AC/DC de Doble Etapa

A pesar de las buenas características que presenta el convertidor de dos etapas su principal

inconveniente es la complejidad puesto que es necesario llevar a cabo el diseño de dos convertidores completos.

#### Ventajas del Control del Factor de Potencia

La importancia de contar con un buen corrector de factor de potencia, es decir, un factor de potencia elevado, se puede entender al observar las siguientes características:

- Reducción de las pérdidas de energía que derivan en una reducción de la factura eléctrica.

- Reducción de la potencia aparente.

- Aumento en el nivel de voltaje en la red de distribución.

- Aumento de la vida útil de las instalaciones.

Aunque también existen desventajas, tales como un mayor coste y complejidad del convertidor y una menor fiabilidad del sistema.

# 1.3. Objetivos del proyecto

La motivación del presente proyecto es la regulación de la tensión de salida de un convertidor conmutado a través de sistemas de control digital en lazo cerrado.

La regulación se realizará mediante la placa de desarrollo proporcionada en el "Actel Fusion Starter Kit" donde se incluye una FPGA que además de contar con módulo digital cuenta con un módulo analógico. Destacar que la placa de desarrollo contiene un único ADC de varios canales, por lo que para una correcta regulación dentro de los límites del convertidor utilizado, será necesario prestar especial importancia a las frecuencias de muestreo cuando se mida más de una señal.

En el capítulo 2 es posible encontrar una descripción a alto nivel de la placa de desarrollo incluida en "Actel Fusion Starter Kit",una descripción detallada de los módulos utilizados, y por último, una descripción de las herramientas software empleadas en el presente proyecto.

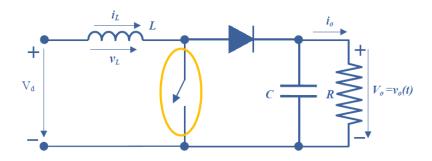

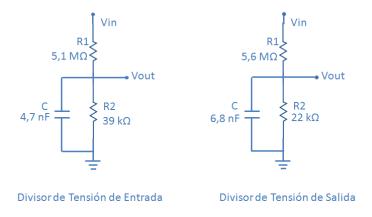

Al igual que se describen las especificaciones de la placa de desarrollo y las herramientas software utilizadas, en el capítulo 3 se incluye la descripción del convertidor conmutado sobre el que se realiza la regulación de la tensión de salida. En concreto, el presente proyecto ha empleado un convertidor boost elevador por medio del cual es posible obtener una tensión de salida superior a la de entrada mediante la utilización de los diferentes estados del pulsador (on/off) que aparece en la figura 1.15.

Figura 1.15: Boost Elevador

A continuación, en el capítulo 4, se detallan las acciones teóricas llevadas a cabo para la regulación de la tensión de salida sobre el convertidor, es decir, la obtención de las funciones de trasferencia mediante la herramienta Matlab y su posterior implementación en lenguaje VHDL.

Mientras que el capítulo 5 se incluyen las simulaciones llevadas a cabo por medio de la herramienta ModelSim para asegurar la correcta implementación del sistema de control, es en el capítulo 6 donde se comprueba su funcionamiento a través de pruebas experimentales.

Finalmente, en el capítulo 7 se incluyen las conclusiones del presente proyecto fin de carrera.

# Tecnología utilizada

Aunque en la actualidad existen múltiples estudios relacionados con el control digital de convertidores conmutados, el presente proyecto tiene como particularidad la realización de este tipo de control utilizando una placa de desarrollo hardware capaz de trabajar con señales mixtas analógico/digital.

La placa de desarrollo hardware utilizada para el desarrollo de este proyecto fin de carrera es la incluida en uno de los kits de FPGAs de uno los principales fabricantes, "Fusion Starter Kit" de Microsemi. Este kit de evaluación cuenta con las ventajas de las FPGAs con señales mixtas, es decir, un único dispositivo que combina lógica programable, RAM, flash y un bloque analógico.

En este capítulo, en primer lugar, se llevará a cabo la descripción de la placa de desarrollo hardware y sus principales elementos. Finalmente se describirán las herramientas software utilizadas en el presente proyecto: Matlab, ModelSim y el conjunto de herramientas incluidas en Libero IDE.

# 2.1. "Fusion Starter Kit"

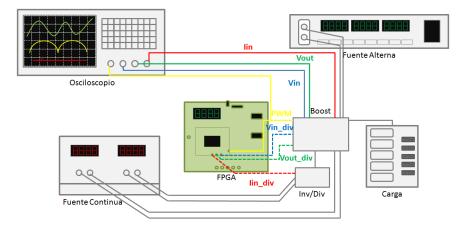

Figura 2.1: Sistema Típico

Como se puede observar en la figura 2.1, la tecnología Fusion utilizada en el presente proyecto es capaz de proporcionar señales mixtas, robustas y flexibles, con un alto rendimiento. En concreto, la FPGA incluida en "Fusion Starter Kit" [23] integra memoria flash, funcionalidades analógicas, SRAM no volátil y lógica programable. Todo ello permite el diseño de sistemas totalmente personalizables y de sencillo uso.

Fusion incorpora la estructura de eficacia probada de las FPGAs de Microsemi. Concretamente, esta tecnología posee una circuitería de señal mixta con miles de compuertas que permiten implementar funciones como el manejo de potencia, generadores de reloj, controladores de motores y cargadores de batería inteligentes, además de las aplicaciones típicas de las FPGAs.

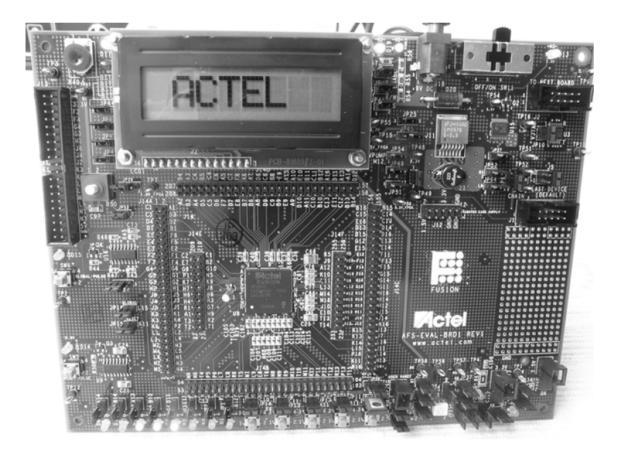

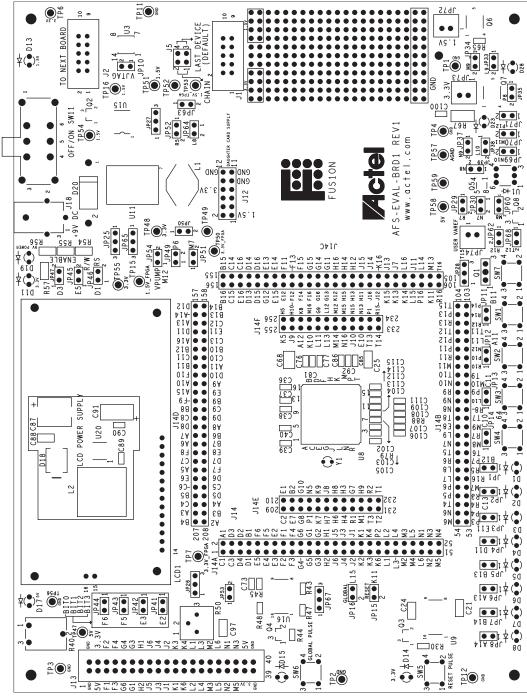

Figura 2.2: Fusion Starter Kit

Tal y como se observa en la figura 2.2, dentro del "Fusion Starter Kit" utilizado para el presente proyecto fin de carrera es posible encontrar:

- FPGA AFS600 con encapsulado FG256

- 600.000 puertas, 512 kB de memoria flash y 108 kB de SRAM

- Periféricos entre los que se encuentran temporizadores, Conversor Analógico a Digital,

Conversor Digital a Analógico y recursos analógicos adicionales.

- Regulador de tensión.

- Pines para la conexión de tarjetas externas que permiten la utilización de sistemas desarrolladas por Microsemi, clientes o terceras partes.

- Cabezales de programación In System Programming (ISP) y Joint Test Action Group (JTAG).

- Oscilador RC, circuito capaz de producir una señal periódica a la salida sin tener ninguna entrada periódica.

- Oscilador de Cristal, oscilador armónico (salida senoidal) cuya frecuencia está determinada por un cristal de cuarzo.

- Lazos de seguimiento de fase capaces de distribuir, manipular y generar la señal de reloj.

- Pantalla de cristal líquido.

- LEDs multicolor.

Para mayor información sobre la placa de desarrollo utilizada acudir al anexo 7.2.

## 2.1.1. Bloque Digital

Dentro de los elementos incluidos en el bloque digital de la placa de desarrollo utilizada [24], el presente proyecto ha utilizado:

- Un oscilador RC con una frecuencia de trabajo de 100 MHz.

- $\bullet$  Divisor de frecuencia de Reloj para obtener frecuencia de inicialización del ADC (10 MHz).

- Pines de entrada y salida (I/O) que han permitido la validación de los resultados con la ayuda de herramientas de visualización.

- Pulsadores para la validación de resultados.

- Memoria flash para la carga de los archivos de configuración del bloque analógico.

- Módulo JTAG (IEEE 1532) para la programación de la placa de desarrollo.

## 2.1.2. Bloque Analógico de la FPGA AFS600

Aunque el bloque analógico incluido dentro de la FPGA AFS600 [25] [26] incluye los elementos listados a continuación, el presente proyecto únicamente ha hecho uso del ADC (ver apartado 2.1.2) utilizando una resolución de 12 bits:

- Analog to Digital Converter (ADC) con frecuencia de muestreo de hasta 600 KHz.

- Digital to Analog Converter (DAC) con frecuencia de muestreo de hasta 600 KHz.

- Resoluciones de 8,10 ó 12 bits.

- Prescaler automático que permite entradas de -11, 5 V hasta +14, 4 V.

- Monitor de temperatura.

- Potenciómetro.

- Entrada de referencia de tensión externa.

El bloque analógico introduce una estructura analógica Quad I/O en la cual cada Quad analógico consta de tres entradas analógicas y un gate driver. La configuración del quad analógico, la resolución del ADC, la secuencia de muestreo de canales y la tasa de muestreo pueden ser programadas e implementadas a través del software integrado en Libero IDE [27], herramienta de Microsemi para la gestión de todo el flujo del diseño, síntesis, simulación y análisis, que será descrita posteriormente. El software utilizado para la configuración del bloque analógico se denomina Analog System Builder (ASB), y al igual que Libero IDE será descrito en el apartado herramientas del presente capítulo.

Es necesario tener en cuenta que la carga de los archivos de configuración del bloque analógico a la FPGA se realiza mediante una memoria flash, en este caso en concreto denominada Flash Memory System Builder (FMSB) [8]. La recomendación de Microsemi para la utilización conjunta del ASB y FMSB es que ambos bloques deben contar con la misma frecuencia de inicialización, la cual en ningún caso deberá sobrepasar los 10 MHz.

Como se ha indicado en el apartado 2.1.1, el presente proyecto utilizará una frecuencia superior a 10 MHz. Por este motivo, se ha incluido un divisor de de frecuencia capaz de obtener la frecuencia máxima de inicialización a partir de la frecuencia del oscilador.

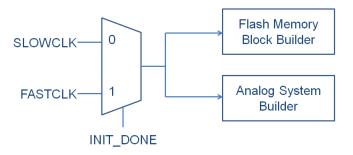

Como se muestra en la figura 2.3, a través de un multiplexor será posible la selección de la frecuencia de reloj de inicialización (SLOWCLK) o la frecuencia de reloj de funcionamiento (FASTCLK).

Figura 2.3: Reloj

Para que no se produzcan fallos, también denominados glitches [29], al llevar a cabo la conmutación de frecuencias una vez finalizada la etapa de configuración, se ha incluido el multiplexor de Microsemi diseñado para tal fin, No Glitch-MUX. Este componte será el encargado de la conmutación de frecuencia a partir de la señal de control la cual será activada una vez haya finalizado la fase de configuración.

## ADC - Conversor Analógico Digital

El presente proyecto ha utilizado el ADC incluido en el bloque analógico para la captura de muestras de tensión sobre un convertidor. La función del ADC será la captura de muestras discretas de un voltaje analógico y continuo obteniendo así una representación binaria y discreta de una determinada señal.

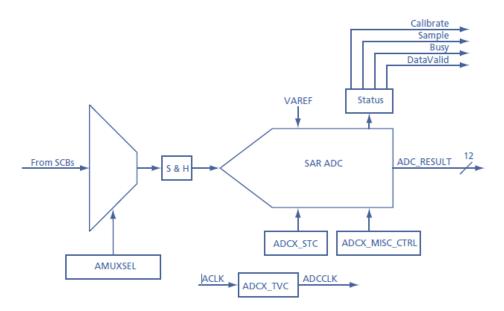

Figura 2.4: Diagrama Bloques ADC

De manera simplificada el ADC queda definido por lo mostrado en la figura 2.4. Como se puede observar, para la utilización del ADC se necesitará la fijación de una tensión de referencia (VAREF) que podrá ser directamente la incluida por defecto (2,56 V) o una referencia externa. También será necesario la definición de la resolución de la salida (ADCRESULTS).

Entre las salidas del ADC se encuentran unas señales de estado que proporcionan información sobre el estado del ADC: Calibrate, Sample, Busy y DataValid.

Como también se aprecia en la figura 2.4, el convertidor utilizado por este ADC se encuentra dentro del grupo de los denominados convertidores de aproximaciones sucesivas, Successive Approximation Register (SAR), los cuales se basan en el uso de un algoritmo de búsqueda por aproximaciones sucesivas aplicado sobre un convertidor digital analógico, DAC, y un comparador, para encontrar, tras varias iteraciones, el código digital de N bits que mejor representa la señal analógica de entrada.

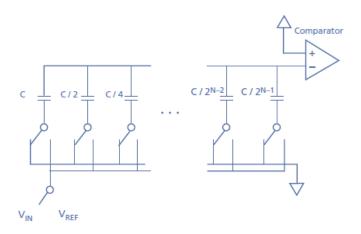

Figura 2.5: Diagrama SAR del ADC

En concreto, el ADC integrado en la FPGA incluida en Fusion Starter Kit está formado por condensadores en paralelo activados a través de interruptores. Antes de comenzar la conversión analógico a digital, todos los condensadores son descargados para posteriormente aplicar sobre estos la tensión analógica de entrada durante un tiempo de adquisición denominado  $t\_sample$ . Una vez finalizado el tiempo de adquisición, la tensión de entrada es aplicada al comparador donde permanecerá almacenada.

Para determinar el primer bit más significativo, Most Significant Bit (MSB), al primer condensador, C, se le aplica la tensión de referencia, lo que produce que a la entrada del comparador nos encontremos con el siguiente voltaje:

$$Voltajealaentradadelcomparador = -Vin + \frac{Vref}{2} \tag{2.1}$$

en caso de que Vin sea superior a  $\frac{Vref}{2}$ , el MSB, es decir, la salida del comparador, será igual a 1, en caso contrario, será 0.

Si la salida del comparador fue 0, C permanecerá conectado a Vref, en caso contrario será conectado a tierra. Independientemente, a continuación  $\frac{C}{2}$  será conectado a la tensión de referencia para determinar así el siguiente bit más significativo. Esta operación se repetirá hasta obtener el array de 8, 10 ó 12 bits con el binario equivalente a la tensión de entrada.

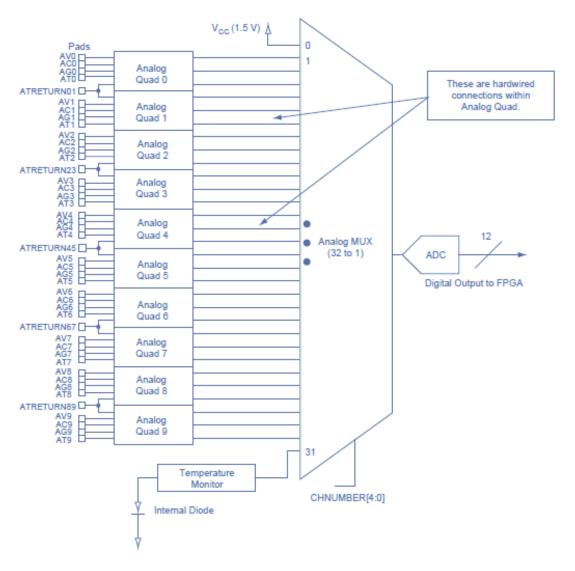

Como se puede observar en la figura 2.6 la entrada analógica del ADC cuenta con un multiplexor 32:1. Mientras que la primera y última entrada a este multiplexor se corresponden con una tensión continua de 1,5 V denominada Vcc y un monitor de temperatura interna, las restante entradas provienen de 10 quads. Cada uno de estos quads contiene tres señales de salida que serán canales de tensión, corriente y temperatura de entrada al multiplexor.

Figura 2.6: Diagrama de bloques del multiplexor de entrada del ADC

Entre las características más importantes del ADC se encuentra el ancho de banda, es decir, el número máximo de conversiones por segundo que es capaz de realizar. Para poder determinar el ancho de banda es necesario conocer los tiempos de adquisición y conversión en cada diseño.

Antes de mostrar las ecuaciones a partir de las cuales es posible obtener los tiempos de adquisición y conversión es necesario conocer el periodo de reloj del DAC (adc clock period), el cual se encuentra definido por:

$$adc\,clock\,period = \frac{1}{ADCCLK} \tag{2.2}$$

donde:

$$ADCCLK = \frac{SYSCLK}{4(1+TVC)} \tag{2.3}$$

SYSCLK es la frecuencia del sistema y TVC es el contenido del valor de registro ADCx\_TVC utilizado para asegurar que la frecuencia de reloj ADC no exceda 10 MHz ni caiga por debajo de 0,5 MHz.

A continuación, se procede a la definición de los tiempos de adquisición y conversión mencionados con anterioridad.

## Tiempo de adquisición

El tiempo de adquisición especifica el tiempo de carga del condensador por la señal analógica de entrada y se encuentra definido por la siguiente ecuación:

$$t \quad sample = (2 + STC)(adc clock period)$$

(2.4)

donde STC es el control del tiempo de adquisición y puede tomar valores entre 0 y 255.

# Tiempo de Conversión

Durante el proceso de conversión se experimentan tres fases: muestreo, distribución y postcalibración. El tiempo de cada una de estas fases debe tenerse en cuenta para el cálculo del tiempo de conversión, definido, como el tiempo total necesario para convertir una entrada analógica en una salida digital.

$$t \ conv = t \ sync \ read + t \ sample + t \ distrib + t \ post \ cal + t \ sync \ write$$

(2.5)

Durante la fase de distribución el ADC obtiene el valor digital equivalente al que se encuentra en el condensador. Este tiempo de distribución depende de la resolución, es decir, el número de bits de la señal de salida, y su función viene dada por:

$$t\_distrib = (Resolution)(adc clock period)$$

(2.6)

La fase de post-calibración es opcional. Actel recomienda activar esta fase para compensar las pérdidas y los efectos de la temperatura. EL tiempo de post-calibración es igual a:

$$t_post_cal = 2(adc clock period) (2.7)$$

Por último, t\_sync\_read y t\_sync\_write son el tiempo transcurrido hasta obtener la señal de entrada o la de salida, esta última, una vez realizada la conversión. Ambos tiempos vienen dados por:

$$t \ sync \ read = t \ sync \ write = sys \ clk \ period$$

(2.8)

donde sys clk period es el periodo de la interfaz del reloj y oscila entre 10 ns y 250 ns.

Se debe tener en cuenta que, si la señal cambia más rápidamente que la frecuencia de muestreo, la información se pierde durante la conversión. Basándose en el teorema de muestreo de Nyquist-Shannon, la tasa mínima de muestreo debe ser al menos el doble de la frecuencia de la componente de frecuencia más alta de la señal objetivo (Frecuencia de Nyquist), proporcionando así suficientes muestras para representar adecuadamente la señal de entrada.

# 2.2. Herramientas Software Utilizadas

A continuación se describen cada una de las herramientas software utilizadas para la realización del presente proyecto.

# 2.2.1. Matlab

La primera de las herramientas utilizadas ha sido MatLab [30]. Se trata de un entorno informático de análisis numérico y representación gráfica de fácil manejo que permite crear funciones propias y programas especiales en código MatLab.

${\it MatLab}$  permite el desarrollo de aplicaciones para la resolución de problemas de múltiples áreas. Entre sus utilidades se encuentran:

- Cálculo matricial y álgebra lineal.

- Polinomios e interpolación.

- Regresión y ajuste de funciones.

- Ecuaciones diferenciales ordinarias.

- Integración.

- Funciones y gráficos en dos y tres dimensiones.

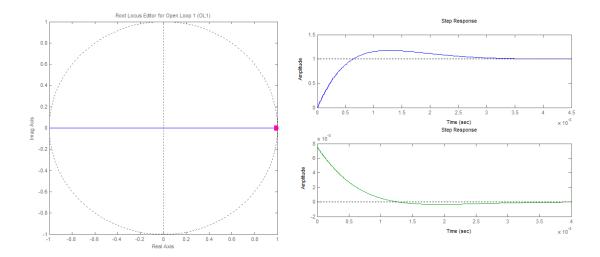

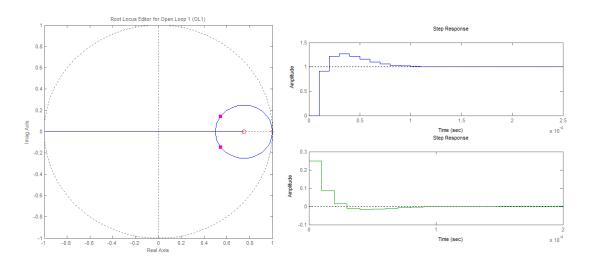

Además, *Matlab* incluye una herramienta gráfica denominada *Sisotool* que facilita en gran medida el diseño de controladores [31]. Es por ello, que el presente proyecto ha utilizado esta herramienta para la obtención de las funciones de transferencia utilizadas para cada uno de los lazos.

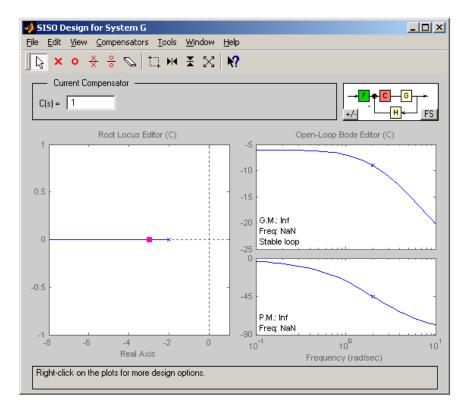

#### Sisotool

Sisotool es una herramienta que trabaja de forma gráfica usando el método del lugar geométrico de las raíces, lo que permite un rápido análisis de las mismas al detectar la situación de los polos y los ceros de un sistema [32].

Figura 2.7: Sisotool

En la figura 2.7 se muestra la ventana de *Sisotool*. A la izquierda, el lugar de las raíces del sistema a analizar cuando realimentamos el sistema bajo estudio. A la derecha, el diagrama de Bode en lazo abierto, tanto de amplitud como de fase.

Mientras los polos y ceros del sistema en lazo abierto se muestran como x y  $\circ$  respectivamente, los polos en lazo cerrado se muestran cómo  $\square$ .

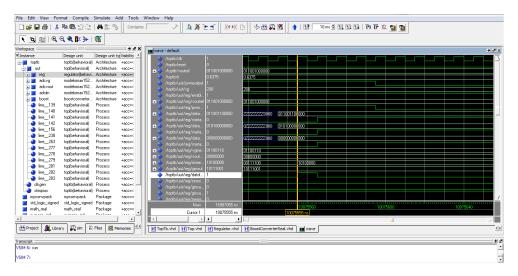

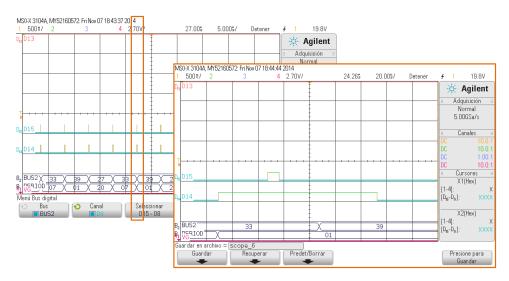

#### 2.2.2. ModelSim

Modelsim [33] es un software que administra un entorno que permite editar, compilar, simular y depurar diseños de sistemas digitales descritos en VHDL [34] y Verilog [35] entre otros. Es por ello, que tras la implementación en VHDL de las funciones de transferencia obtenidas mediante la herramienta Matlab, se ha utilizado Modelsim para la depuración y simulación de los sistemas de control implementados.

Figura 2.8: ModelSim

Como se muestra en la figura 2.8, la ventana principal de esta herramienta se encuentra dividida en tres áreas:

- Componentes: en este cuadro se muestran todos los componentes que forman parte del diseño así como las librerías utilizadas.

- Simulación o waveform: se muestra el valor de las señales añadidas durante el tiempo que se ha corrido la simulación.

- $\bullet$  Consola: mediante línea de comando nos permite ejecutar cualquier operación que Modelsim sea capaz de realizar, como añadir y eliminar señales de la simulación, ejecutar, compilar

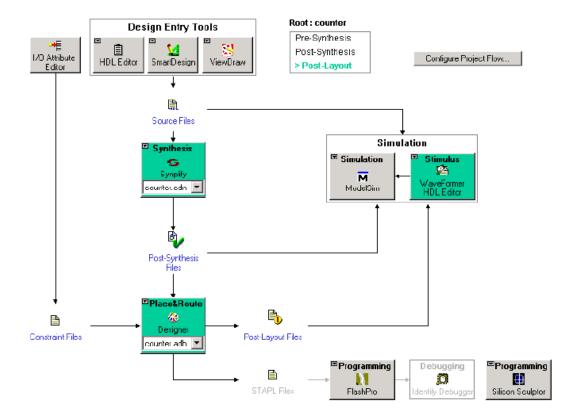

#### 2.2.3. Libero IDE

Para apoyar a la tecnología Fusion, Microsemi cuenta con una serie de herramientas que ayudan a maximizar la productividad del diseño. El entorno de diseño integrado, Integrated Design Environment (IDE), permite a los diseñadores crear instancias y configurar periféricos fácilmente, establecer vínculos entre los periféricos, crear o importar bloques de construcción o diseños de referencia y realizar la verificación de hardware. Además, esta suite de herramientas también añade características de depuración de hardware/software.

Figura 2.9: ProjectFlowWindow

En concreto, Libero IDE [27] es el software de Microsemi utilizado para la gestión de todo el flujo del diseño, síntesis, simulación y análisis. Todas la herramientas que intervienen en el proceso de diseño pueden observarse desde la *Project Flow Window* que aparece en la figura 2.9.

Dentro de *Project Flow Window* se encuentra *Smartdesign*, una herramienta que actúa de pizarra para bloques funcionales. Además de permitir el montaje e interconexión de bloques funcionales, también permite agregar componentes desde el catálogo y componentes creados por el diseñador sobre diferentes lenguajes HDL: VHDL o Verilog.

Una vez finalizado el diseño, es necesario ejecutar la herramienta de síntesis *Symplify* [36] [37], la cual lleva a cabo una síntesis de alto nivel, es decir, crea una lista de conexiones del diseño o *Netlist*.

A continuación, la herramienta Designer llevará a cabo el Place & Route. Este proceso es el encargado de asignar lugares y recursos físicos de la FPGA a la Netlist creada en el paso anterior. Una vez realizado el Place & Route se creará un archivo binario con toda la información, listo para ser descargado en la FPGA.

La programación de la FPGA "Fusion Starte Kit" se realiza mediante una combinación del software FlashPro [33] [34] y el hardware de programación. Para llevar a cabo la programación únicamente será necesario la conexión de la memoria flash a un PC y a la placa de destino.

Por último, Libero IDE también permite llevar a cabo la verificación del diseño mediante una simulación funcional través del simulador integrado, ModelSim de Mentor Graphics.

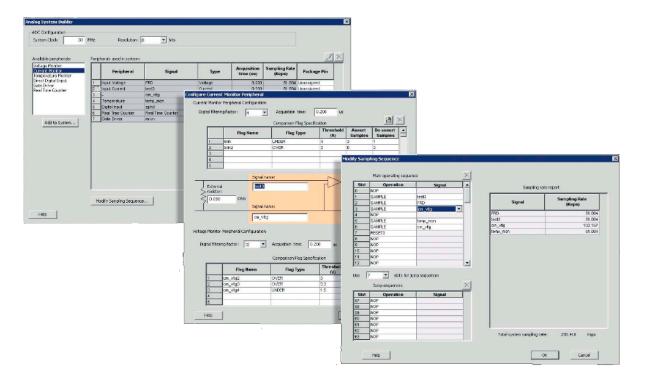

## ASB - Analog System Buider

Como se observa en la figura 2.10 ASB [30] es una herramienta a través de la cual se lleva a cabo la configuración del bloque analógico completo de la FPGA incluida en Fusion Starter Kit.

Figura 2.10: Analog System Builder

Algunas de las posible acciones que se pueden llevar a cabo se listan a continuación:

- Elegir el número de canales de entrada analógica que se desea monitorear.

- Elegir el tipo de cada canal de entrada.

- Elegir el número de canales de salida analógica.

- Especificar la ubicación de cada canal.

- Definir el orden de muestreo requerido.

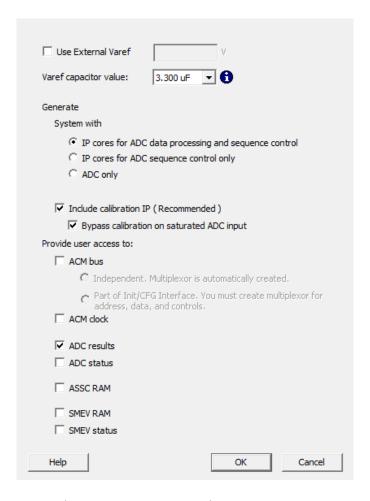

Las opciones avanzadas de ASB además de ajustar la tensión de referencia externa permite generar configuraciones personalizadas (observar figura 2.11).

En concreto, el uso de un voltaje externo de referencia, permite al ADC realizar conversiones más precisas. En caso de no introducir un voltaje de referencia, por defecto se utiliza Voltaje de Referencia (Vref) igual a 2,56V.

Por otro lado, dentro de las configuraciones personalizadas del ASB se encuentran tres modalidades:

- IP Cores for ADC data processing and sequence control.

- IP Cores for ADC Sequence control.

- ADC only.

IP Cores for ADC data processing and sequence control permite la secuenciación, generación de banderas, promedio de datos y, en general, la gestión del ADC sin casi intervención del usuario.

Figura 2.11: Analog system Buider Advanced Option Dialog Box

$IP\ Cores\ for\ ADC\ Sequence\ control$ instancia únicamente el bloque analógico y la memoria RAM

Por último, ADC only omite el procesamiento de datos, la secuenciación y las funciones de gestión del ADC de manera que es el propio usuario quien debe manejarle por completo. De este modo, el usuario deberá declarar las señales de entrada listadas a continuación.

- ADCSTART. Indica el comienzo de la conversión.

- ADCRESET. Restablece y desactiva el bloque analógico.

- PWRDWN. Cuando está activo, el bloque analógico se apagará mientras la parte digital sigue en funcionamiento.

- MODE[3:0]. Este registro, además de controlar la resolución de ADC Result, controla la calibración y el apagado después de cada conversión.

- STC[7:0]. Control para la división del reloj.

- TVC[7:0]. Control del tiempo de muestreo.

- CHNUMBER. Selecciona el canal de trabajo.

Las salidas obtenidas del bloque analógico serán por tanto:

- DATAVALID. Indica la finalización de la conversión.

- CALIBRATE. Indicador de estado de la calibración.

- BUSY. Indicador de estado de la ocupación.

- ADCRESULT. Proporciona el resultado binario obtenido de la medición de la señal analógica en 8, 10 ó 12 bits.

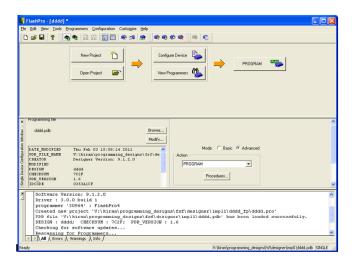

#### FlashPro

Para llevar a cabo la programación de la FPGA es necesaria la utilización de la interfaz gráfica de FlashPro [38] [39]. Como se puede observar en la figura 2.12 la interfaz gráfica de usuario está compuesta por una ventana de configuración de dispositivos y una ventana de registros que muestra la información de programación, mensajes de error y mensajes de advertencia.

Figura 2.12: Interfaz Gráfica FlashPro

# Convertidor Boost Elevador

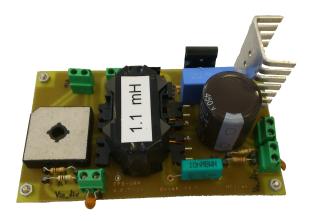

El presente proyecto llevará a cabo la regulación de la tensión de salida de una fuente conmutada, en concreto, de un convertidor boost elevador. Por ello, este capítulo se centra en descripción de los estados de operación del convertidor utilizado: modo de conducción continuo y modo de conducción discontinuo, los cuales nos permitirán comprender su funcionamiento.

En último lugar, se describirán las características del boost utilizado.

# 3.1. Convertidor Boost Elevador

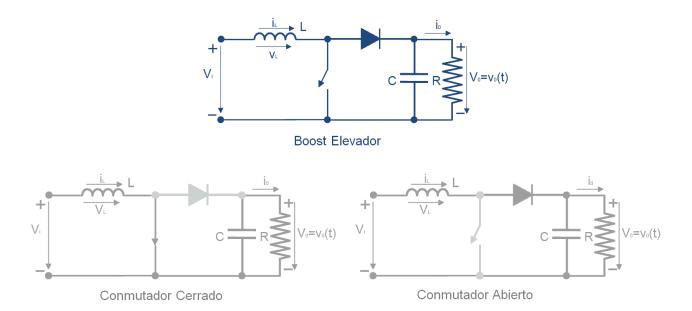

La verdadera eficacia de las fuentes conmutadas radica en el apagado y encendido del interruptor o conmutador de manera que las pérdidas obtenidas sean minimizadas en la medida de lo posible. Por ello, no es de extrañar que el principio básico de estas fuentes consista en la posibilidad de obtener estados distintos dependiendo del estado del conmutador (ver figura 3.1).

Para el caso concreto del Boost Elevador [40], donde el voltaje promedio de la salida es mayor que el voltaje promedio de la entrada, existen diferentes estados de operación:

- Modo de Conducción Continuo (MCC). La corriente que atraviesa la bobina varía entre unos valores máximo y mínimo, pero nunca llega a anularse.

- Modo de Conducción Discontinuo (MCD). La corriente que atraviesa la bobina se hace nula en un momento determinado a lo largo de un intervalo de tiempo durante el cual el interruptor está abierto.

De manera simplificada, el funcionamiento del Boost Elevador es el siguiente [41]. La energía precedente de la entrada es conducida por el elemento de conmutación para ser almacenada en la bobina. Este almacenamiento de energía únicamente se produce durante el periodo de conducción del interruptor, no existiendo transferencia de energía a la carga.

Por el contrario, la apertura del interruptor ocasiona que la energía acumulada en la bobina se transfiera a la carga. Para que la corriente disminuya la tensión en la bobina tiene que ser negativa, y por ello, la tensión de salida es mayor que la de entrada.

Figura 3.1: Boost Elevador

#### 3.1.1. MCC - Modo de Conducción Continuo

El Modo de Conducción Continuo [42] se caracteriza porque la corriente que atraviesa la bobina  $(i_L)$  nunca se anula. Esto quiere decir que cuando el conmutador se encuentra cerrado, la bobina se encuentra en un estado de carga gracias a esta corriente. Cuando el conmutador permanece abierto, la corriente de la bobina se descarga a través de la carga sin llegar a vaciarse la energía acumulada en la bobina.

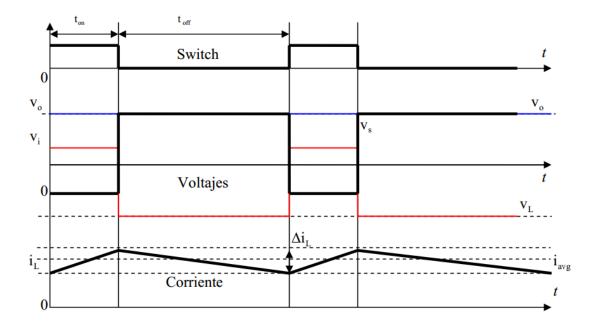

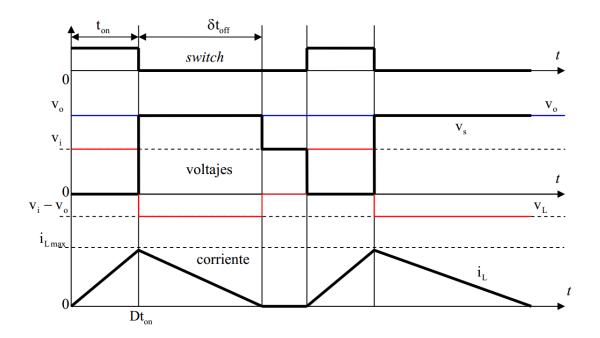

En la figura 3.2 se pueden observar las típicas formas de onda del Boost Elevador operando en MCC.

En la parte superior se muestra la forma de onda del conmutador.  $t_{on}$  es el periodo de tiempo que el conmutador se encuentra cerrado, por el contrario,  $t_{off}$  es el periodo de tiempo que este se encuentra abierto.

También es posible encontrar las formas de onda de los voltajes  $V_i$ ,  $V_o$ , y  $V_L$  que se corresponden con los voltajes a la entrada, a la salida y en la bobina.  $V_s$  es la diferencia de potencial en el interruptor.

En último lugar se observa la forma de onda de la corriente  $i_L$  de la bobina. Esta, muestra sus dos etapas: la etapa de carga y la etapa de descarga. El rizado  $\triangle i_L$  es la diferencia de la corriente máxima y mínima. El valor medio de la forma de onda de  $i_L$  es  $i_{avg}$ .

Cuando el conmutador permanece cerrado, la tensión de la bobina  $V_L$  corresponde con la tensión de entrada  $V_i$ , y en consecuencia, la corriente en la bobina  $i_L$  sufre un incremento lineal positivo.

$$\frac{\triangle i_L}{\triangle t} = \frac{V_i}{L} \tag{3.1}$$

Al final de la etapa de carga en la bobina, el incremento de la corriente a través del inductor está dada por la siguiente ecuación, donde D es igual al

$$\Delta i_{Lon} = \int_0^{DT} \frac{V_i}{L} dt = \frac{V_i \cdot D \cdot t_{on}}{L}$$

(3.2)

Figura 3.2: Formas de onda en MCC

Cuando el conmutador permanece abierto, la tensión en este  $(V_s)$  pasa a ser positiva e igual a la tensión de salida, y el voltaje en la bobina  $(V_L)$  pasa a ser negativo, lo que se traduce en un cambio en la polaridad de la bobina.

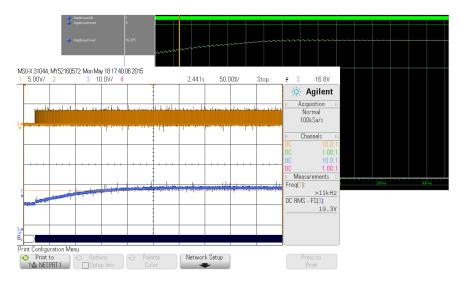

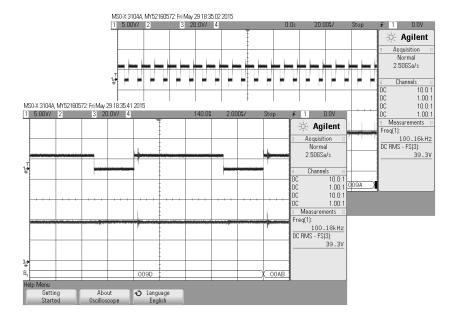

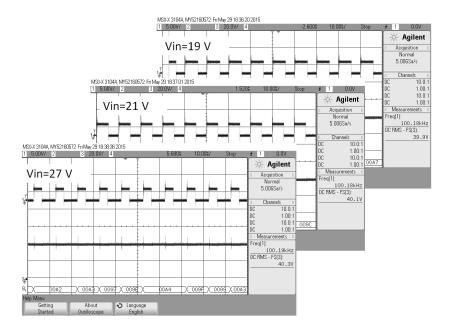

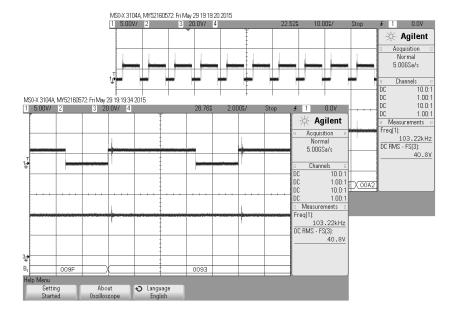

La corriente en la bobina  $(i_L)$  sufre un decremento lineal producido por la descarga de energía que sufre debido a la carga.