### Relación entre Velocidad y Consumo en FPGAs

E. Todorovich, G. Sutter y N. Acosta INCA, Universidad Nacional del Centro, Tandil, Argentina etodorov@exa.unicen.edu.ar http://www.exa.unicen.edu.ar

E. Boemo y S. López-Buedo

ETS Informática, Universidad Autónoma de

Madrid,

Ctra. Colmenar Km.15, Madrid, España

<a href="http://www.ii.uam.es">http://www.ii.uam.es</a>

### Resumen

Existen trabajos en la literatura que muestran que los circuitos con mayor frecuencia máxima de operación son los que menos energía consumen. En este artículo se trata de verificar experimentalmente esta proposición para FPGAs, lo cual abre una posibilidad para la estimación y optimización de consumo frente a la falta de herramientas EDA de diseño para bajo consumo para dispositivos programables.

#### **Abstract**

There is bibliography that shows that the circuits with the maximum operation frequency, consumes the less energy. In this paper this proposition is verified experimentally for FPGAs, opening a possibility for power estimation and optimization, taken into account the lack of EDA tools for low power design for programmable devices.

### 1. Introducción

Actualmente, el consumo es, para los diseñadores de circuitos digitales, un parámetro tan importante como el área y la velocidad [1]. Esto se debe principalmente al éxito de los dispositivos portátiles, que exigen aumentar el tiempo de servicio mientras se reduce el tamaño y el peso de los equipos. Igualmente, para cualquier chip se trata de reducir los costos de la fuente de alimentación, del encapsulado y accesorios para refrigeración, mientras se minimiza la tasa de fallas y se maximiza el factor de integración. También se pueden considerar todos los beneficios desde el punto de vista del cuidado del medio ambiente que surgen como consecuencia de

obtener un dispositivo con bajo consumo de energía. Para el caso particular de las FPGA, una disminución en el consumo puede permitir mayores niveles de utilización y una velocidad de operación superior.

Sin embargo los diseñadores de sistemas basados en FPGAs cuentan con herramientas para optimizar los circuitos en área y velocidad, pero a pesar de los resultados obtenidos en la investigación realizada en los últimos años [2][3], los IDE (Integrated Development Environment) de los fabricantes de FPGAs no proveen software de diseño para bajo consumo. Nótese que la alternativa de medir el consumo de una FPGA montada en una tarjeta suele no ser viable por ser la FPGA, normalmente, un componente de un sistema mayor, integrado en las últimas etapas de desarrollo. Y aunque esta medición fuera posible se trata, como principio general de diseño, de estimar y optimizar el consumo de un circuito desde las primeras fases de diseño.

Frente a esta falta de herramientas de diseño para bajo consumo, interesa saber si las herramientas que se proveen y reportes que se generan para área y análisis de tiempo en los IDE de los fabricantes de FPGAs, son útiles también en diseño para bajo consumo. Debido a la falta de correlación entre área y consumo en FPGAs observada en [4], en el presente trabajo sólo se analiza la relación entre frecuencia máxima de operación y consumo. Esta relación fue considerada por investigadores y fabricantes de ICs. Por ejemplo Xilinx recomienda rediseñar los circuitos haciéndolos más rápidos para disminuir su consumo, más allá de que la velocidad pedida en las especificaciones de diseño se haya obtenido [5]. En particular, al optimizar los

| Test    | Topology       | Reference | Description | Number of | Logic depth in the |

|---------|----------------|-----------|-------------|-----------|--------------------|

| circuit |                |           | language    | CLB       | critical path      |

| Set A   | Foundation 2.1 | -         | VHDL        | 54        | 12 LUTs            |

|         | Synthesis      |           |             |           |                    |

| Set B   | Wallace        | [8]       | VHDL        | 69        | 13 LUTs            |

| Set C   | Hatamian       | [9]       | Gate level  | 96        | 15 LUTs            |

| Set E   | Guild          | [10]      | VHDL        | 60        | 15 LUTs            |

Tabla I: Principales características de los circuitos de prueba sintetizados para el dispositivo XC4010PC84-4C

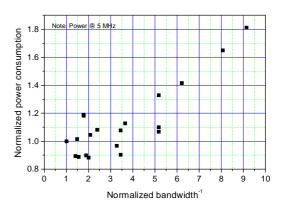

parámetros de los que depende la velocidad, como el fanout, la cantidad de CLBs o la profundidad de lógica, se optimiza el consumo de un circuito. En [6] se ha estudiado el efecto de la segmentación y el particionado manual en multiplicadores sobre velocidad y consumo. Los resultados de este trabajo muestran que estas acciones no sólo aumentan la velocidad de operación de los multiplicadores, sino que también se reduce el consumo para una velocidad de operación fija (Fig. 1).

La optimización de un parámetro de un IC como la velocidad, se puede atacar en diferentes niveles en el ciclo de diseño. A nivel de topología, se puede disponer de varias alternativas funcionalmente equivalentes. Por ejemplo para la adición binaria se tiene los sumadores ripple-carry, carry-save, carryskip, carry look-ahead, Brent & Kung, etc. Cada una de estas alternativas tiene sus propios valores de ATC (Area-Time-Consumption) en una tecnología dada. Una vez seleccionada una topología, se pueden modificaciones arquitectónicas aplicar paralelismo o segmentación. Por último, el circuito puede ser transformado a nivel físico: particionado manual, floorplaning, selección de un valor para el esfuerzo de rutado, restricciones de tiempo (timming constraints), etc.

En este trabajo se exploran alternativas topológicas y físicas para multiplicadores implementados en FPGAs de la serie 4000 de Xilinx. En la sección 2 se resumen las principales características de los circuitos que se estudiaron y los detalles de realización de los experimentos. En la sección 3 se presentan y analizan los resultados obtenidos. Finalmente se presentan conclusiones y recomendaciones de diseño para reducir el consumo en FPGAs.

### 2. Circuitos de Prueba

La relación entre velocidad y consumo y la incidencia de las diferentes decisiones de diseño planteadas en este trabajo se estudian sobre cuatro tipos de multiplicadores. Además de existir bibliografía que estudia este tipo de circuitos a lo largo de toda la historia de la computación, se pueden materializar sobre diferentes topologías lo cual convierte a los multiplicadores en casos de prueba apropiados [8] [9] [10]. Las principales características de cada tipo de multiplicador se resumen en la tabla I. En estos experimentos se incluye un multiplicador que resulta de la síntesis de un modelo VHDL de alto nivel (p <= a \* b, donde a y b son las entradas y p la salida del multiplicador).

**Fig.1:** Relación ancho de banda- consumo para multiplicadores segmentados. Datos obtenidos de [6].

Todas las medidas experimentales fueron realizadas en las mismas condiciones sobre una FPGA *XC4010PC84-4C* de Xilinx. Por este motivo todos los prototipos tienen prácticamente las mismas componentes de potencia estática y externa (*off-chip*). Como estas componentes del consumo no se pueden manipular en ningún momento del diseño

para FPGA, se aíslan y no se consideran en los gráficos, para centrar el estudio en la componente dinámica del consumo.

La técnica usada en este trabajo para aislar las distintas componentes del consumo fue propuesta en [6]. Otra alternativa puede verse en [7].

Según [6], la componente estática se puede medir dejando las entradas de la parte combinatoria fijas sin actividad en el reloj, luego de haber configurado la FPGA. Para aislar la componente externa de consumo el circuito se mide dos veces. Primero en normales de condiciones operación, deshabilitando los buffers de tres estados en las salidas. De esta manera, la componente off-chip se puede aproximar mediante la diferencia entre estos dos resultados. Finalmente, para que quede solamente la potencia dinámica de la parte combinatoria. resta aislar la potencia sincronización que se puede calcular diferencia, midiendo el consumo con el circuito sin actividad en las entradas, mientras opera la señal de reloj normalmente, de manera que sólo el árbol de reloj tenga actividad.

Para estudiar, a nivel de diseño físico, la incidencia de los parámetros de los algoritmos de emplazamiento y rutado, se realizaron 100 implementaciones de cada multiplicador usando un proceso automático provisto en el software del fabricante. De este conjunto de implementaciones se tomo una muestra de 21 casos que fueron los que se midieron, seleccionados de manera de tener las implementaciones más rápidas, las más lentas y las de velocidad media.

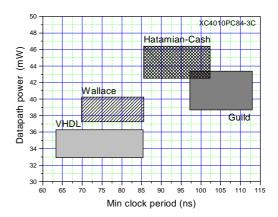

Fig.2: Potencia dinámica de los cuatro multiplicadores de 8 bits medidos.

### 3. Resultados Experimentales

## 3.1 Correlación Velocidad-Consumo. Efecto de las diferentes topologías

Cada topología tiene sus propias características en cuanto a área y velocidad. Para obtener un circuito con bajo consumo, debe elegirse la topología que

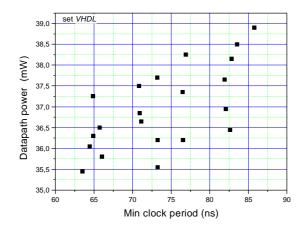

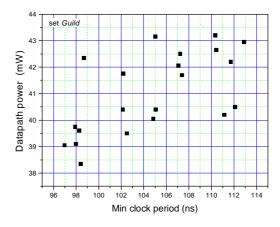

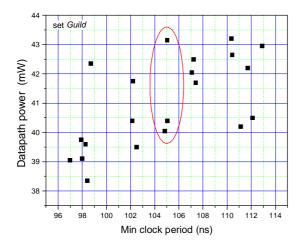

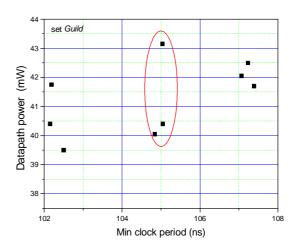

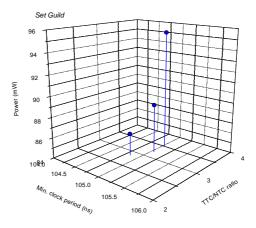

**Fig. 3**: Relación velocidad-consumo dentro de la misma topología: VHDL (izquierda) y Guild (derecha). Componente dinámica de potencia medida a 2 MHz.

presente los menores valores de este parámetro. En la figura 2 se muestran los resultados de las medidas de los cuatro conjuntos de multiplicadores, donde cada región rectangular incluye los valores obtenidos de las 21 implementaciones seleccionadas, que se diferencian en los parámetros de emplazamiento y rutado usados durante la síntesis.

El eje de las abscisas en la Fig. 2, muestra el mínimo período de operación, que es la inversa de la máxima frecuencia admitida por el circuito. Este valor se obtiene de los reportes generados durante la síntesis. Es importante aclarar que el consumo de la FPGA fue medido en todos los casos, con el dispositivo operando a 2 Mhz, independientemente de la frecuencia máxima de operación, que indica cuan rápido es el circuito.

La potencia dentro de cada conjunto de circuitos del mismo tipo varía en un factor de aproximadamente 1.1, y la máxima variación para todos los circuitos medidos es de 1.3.

# 3.2. Correlación Velocidad-Consumo para implementaciones dentro de la misma topología

Para un mismo tipo de multiplicador, es decir, luego de haber seleccionado una topología, la diferencia entre las distintas implementaciones está en el emplazamiento y el conexionado de los CLBs.

En la Fig. 3 se muestran los resultados obtenidos para el multiplicador Guild y el descrito en VHDL comportamental. Si bien se observa dispersión de los puntos en los gráficos, vale la suposición planteada: los circuitos rápidos son los que menos consumen. Los coeficientes de regresión son 0.63 y 0.65 respectivamente.

Por ejemplo, de las 12 implementaciones con el menor período mínimo de operación, o sea las más rápidas, 10 tienen un consumo menor que la media. Para el multiplicador tipo Guild, 9 de las 10 implementaciones más rápidas, presentan un consumo menor que el valor medio.

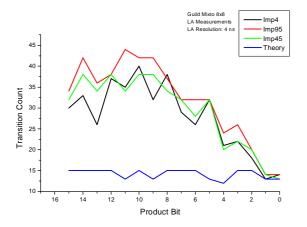

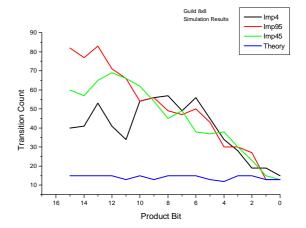

### 3.3. Importancia de los glitches

Mediante los experimentos reportados en esta sección se trata de explicar las fluctuaciones observadas en la relación velocidad-consumo. Esto realiza analizando los glitches que se producen en los circuitos. Para ello estudiaron algunas se implementaciones para cada tipo de multiplicador. Las implementaciones analizadas fueron seleccionadas de manera que tengan casi el mismo periodo mínimo de operación (PMO) y la mayor

Fig.4: Estudio de las fluctuaciones en el consumo para circuitos de similares velocidades (Multiplicador Guild).

Fig.5: Transiciones a la salida de los multiplicadores seleccionados. Cuenta obtenida por medición (izquierda) y por simulación (derecha)

fluctuación de consumo entre ellas. Por ejemplo para el multiplicador tipo Guild se seleccionaron las 3 implementaciones que se ven en la Fig. 4.

Como las implementaciones originales tenían sus salidas registradas, se sacaron los FF de la salida usando el *FPGA Editor* de manera que no se altere el resto de la implementación. Luego se uso un analizador lógico para contar todas las transiciones a la salida para una serie de 16 pares de operandos que generan máxima actividad a la salida. Sin embargo, como la resolución del instrumento es de 4 ns, los valores obtenidos son una cota inferior de los verdaderos, aunque se supone que el porcentaje de error se mantiene constante para poder comparar los resultados obtenidos por este método. Además de realizar estas mediciones, se hizo un estudio idéntico en simulación. Los resultados se muestran en la Fig. 5.

Para resumir esta información se calcula la cantidad de transiciones por operación (TPO) según la Ec.1. En la Fig. 6 se muestra el cociente entre la cuenta de TPO total obtenidas por simulación (TTC) y la cuenta de TPO necesarias si no hubiera *glitches* (NTC), es decir, en un modelo con demora cero.

$$TPO = \frac{Trn\_Count}{Number\_of\_Oper}.$$

EC. 1: Transiciones por operación.

**Fig. 6:** Relación entre actividad a la salida de los multiplicadores y consumo para implementaciones con similar velocidad.

Viendo la Fig. 6 se nota que la cuenta de transiciones se puede usar para detectar el circuito con menor consumo tomados de un conjunto de implementaciones con velocidades prácticamente iguales.

### 4. Conclusiones

En este trabajo se estudiaron algunas de las alternativas accesibles para los usuarios del software de los fabricantes de FPGAs cuando tratan de obtener diseños con menor consumo de energía. La idea es que el usuario pueda emplear las herramientas e información disponible a partir de los reportes de temporización generados durante el ciclo de diseño para, indirectamente, mejorar el consumo. Estas recomendaciones se pueden complementar con las propuestas en un reciente trabajo para el nivel arquitectónico [11].

Las conclusiones y recomendaciones más importantes que se pueden dar a partir de este trabajo son:

- Las topologías con menores períodos mínimo de reloj, son las que menos consumen.

- Lo mismo vale dentro de una topología seleccionada y esta optimización puede obtenerse solamente ejecutando un número de veces el proceso de emplazamiento y rutado con diferentes parámetros.

- En el caso que se tenga que elegir entre implementaciones con períodos mínimos de operación muy similares, la implementación que presente menor actividad de conmutación es la que obtendrá un ahorro de consumo.

### **Agradecimientos**

Se agradece el soporte brindado por CONICET de la República Argentina a E. Todorovich y G. Sutter. Igualmente, mediante el programa FOMEC (Fondo de Mejora de la Calidad Educativa), se financió las estancias de Acosta, Todorovich y Sutter en la ETS de la Univ. Autónoma de Madrid, donde se hicieron los experimentos.

### Referencias

- [1] Massoud Pedram, "Design Technologies for Low Power VLSI", in Encyclopedia of Computer Science and Technology, vo 36, Marcel Dekker, Inc. 1997, pp 73-96

- [2] F. Najm, "A Survey of Power Estimation Techniques in VLSI Circuits", IEEE Trans. on VLSI Systems, Vol.2, n°4, pp.446-455. Diciembre 1994.

- [3] M. Pedram, "Power Minimization in IC Design: Principles and Applications", ACM Trans. On Design Automation of Electronic Systems", vol.1, n°1, pp.3-56, January 1996.

- [4] E. Todorovich, G. Sutter, N. Acosta E. Boemo and S. López-Buedo, "End-user low-power alternatives at topological and physical levels. Some examples on FPGAs", XV Conference on Design of Circuits and Integrated Systems (DCIS2000), Le Corum, Montpellier, France, November 21-24, 2000.

- [5] Xilinx Inc, "Power Considerations", in "Technical Conference and Seminar Series", 1995.

- [6] E. Boemo, "Contribution to the Design of Fine-grain Pipelined VLSI Arrays", Ph.D. Thesis, ETSI Telecomunicación, Universidad Politécnica de Madrid, 1996.

- [7] L. Mengíbar, M. García, D. Martín, and L. Entrena, "Experiments in FPGA Characterization for Low-power Design", *Proc. DCIS'99*, Palma de Mallorca, 1999.

- [8] C. Wallace, "A Suggestion for a Fast Multiplier". IEEE Trans. on Electronic Computers, pp.14-17, February 1964.

- [9] Hatamian M. and G.L.Cash. "A 70-MHz 8-bit x 8 bit Parallel Pipelined Multiplier in 2.5-um CMOS". IEEE Journal of Solid-State Circuits, August 1986

- [10] H. Guild, "Fully Iterative Fast Array for Binary Multiplication and Addition", Electronic Letters, pp.263, Vol.5, N°12, June 1969.

- [11] A. Garcia, W. Burleson and J. Danger, "Power Consumption Model of Field Programmable Gate Arrays", Proc. FPL'99, in LNCS. Springer-Verlag, 1999.