|

ASIC

and FPGA Design Undergraduate

Courses |

Temario DIE:

Dispositivos Integrados Especializados (ASIC and FPGA Design) |

|

Tema 0: Revisión de VHDL e ISE Objetivo: Clase de Laboratorio inicial

para no perder el escaso tiempo, aun cuando no se ha presentado suficiente

material teórico. Sirve de punto de ruptura con la inercia de los meses de

verano y se aprovecha para recordar la utilización del ISE/Vivado y la

sintaxis VHDL. Tema 1: Introducción a los ASICs

Objetivo: La última parte del

acrónimo FPGA significa Gate Array.

Por ello, es preciso comenzar por esta tecnología semicustom explicando su

origen, ideas, y la jerga microelectrónica. Todos estos aspectos han influido

y se han colado en la tecnología FPGA. ASICs: Application

Specific Integrated Circuit. Proceso de Fabricación. Transistor MOS. Gate Array. Problemas de los masked-ASICs. Tema 2: Introducción a las FPGAs Objetivo: Este tema se desarrolla a

lo largo del curso, pero es necesario un resumen inicial para mitigar la

desorientación de los/las estudiantes en el lab. Básicamente, saber cómo es

aproximadamente por dentro una FPGA y a qué corresponde cada uno de los pasos

que se ejecutan al utilizar la herramienta EDA del lab.

Historia de Xilinx Inc. Ideas para una FPGA: LUTs,

Interconexiones y Memoria de Configuración. Estructura de una LUT. Tipos de Configuración Arquitectura de FPGAs Xilinx: Slices Estándares de I/O y BW. Encapsulados Bloques Embebidos, soft-macros y Cores IP Diagrama de flujo de diseño.

Herramienta EDA, Herramientas de síntesis ad-hoc. Tema 3: Retardos en Circuitos Integrados Objetivo: En tecnología FPGA, el retardo

de una operación lógica está en el orden de decenas de picosegundos mientras

que el de una pista puede alcanzar varios ns. Es

decir, un factor mayor a mil veces. Es evidente que diseñar bajo estas

condiciones (diametralmente opuestas a las que había en el lab de CED de

primero de la EPS UAM) requiere conocer por qué aparecen estos retardos, que

problemas genera y cómo humildemente tratar de mitigarlos, considerando un

modelo RC.

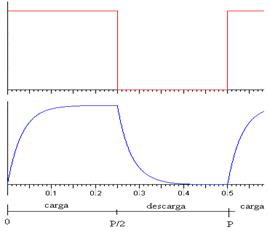

Capacidad. Carga a corriente

constante. Carga a corriente constante. Energía almacenada en un condensador. Valores típicos de C en circuitos

integrados. Retardos intrínsecos y extrínsecos. Fanin y

Fanout. Datos de una célula SC Señales globales (broadcasted) y cómo limitar el fanout de un

circuito Compromiso area-time. Retardos en Xilinx Árbol de Reloj: Diseño en 0.18μ. Distorsión de Duty-Cycle. Digital Clock Manager. Timing Analyzer, false-path y Caminos Críticos (Critical Path) Deration con T y Vdd Miscellaneous: Pull-Up / Pull-Down, Bus keeper Retardos asíncronos Tema 4: Sincronización en Circuitos Integrados Objetivo: Es continuación del tema

anterior. Explica las consecuencias de mezclar millones de FF con frecuencias

de operación de centenas de MHz. Se presenta el árbol de reloj, el principio

de diseño síncrono, los fallos de sincronización y las ideas para enganchar

en fase relojes internos y externos. Si hay tiempo adicional, se estudia la metaestabilidad y la sincronización entre dominios de

reloj.

Actividad espuria (glitches). Glitches en circuitos combinacionales. Registros de sincronización. Parámetros temporales de un FF Gated-clocks: “relojes gateados” Skew (Torcido) de reloj. Valores. Fallos de sincronización: captura

nula y doble captura. Principios de Diseño Síncrono Metaestabilidad. Tema 5: Pipelining

Objetivo: Construir pipelines, el

método más sencillo, directo y potente para acelerar un circuito en FPGA. Fue

tema de investigación en la EPS UAM hasta que las FPGA la transformaron en

una técnica cotidiana de diseño. En el Lab se realiza un multiplicador

pipeline y en la teoría se revisan conceptos y limitaciones. Ideas y Conceptos Básicos Velocidad (Throughput) y latencia. Aceleración (speed-up) y penalización en área. RCA segmentado. Registros de skewing y deskewing Granularidad, Profundidad de Lógica. Coste de un pipeline. Arrays segmentados para multiplicación. Efecto de los retardos de pista y FF

sobre la eficiencia del pipeline. Retiming. Composición del periodo de un pipeline real. Ley de los Rendimientos

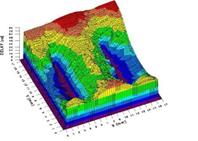

Decrecientes. Comunicación local y global (broadcasted). Tema 6: Algoritmos EDA

Objetivo: Nociones de Síntesis,

Particionado, Emplazamiento y Rutado. No es un tema central en DIE, pero

ayuda al diseñador a entender las opciones que no son default en la herramientas. Netlist. Simplificación.Síntesis, Particionado, Emplazamiento y Rutado. Uso de subexpresiones Cofactoreo de Shanon Método de fuerzas Método de Steimberg Mincut Simulated Annealing Rutado global y detallado Principales opciones de diseño manual

de la Herramienta ISE Tema 7: Diseño para Testabilidad

Objetivo: Al igual que en el tema

anterior, se presentan las ideas primarias de “Testabilidad”. En algunos

casos son importantes, pero en otros, la reprogramabilidad

de las FPGAs permite obviarlas. Bugs en Circuitos Integrados DFT = Design

for Testability. Técnicas Heurísticas y Sistemáticas. Test Exhaustivo Observabilidad y Controlabilidad Modelo Stuck-at.

Cobertura de fallos Test de FSMs: Scan

Path Temperatura y fallos. Chipscope. Instrumental de Verificación. Last update: |